# Instituto Politécnico Nacional

## Centro de Investigación en Computación

# INSTITUTO POLITÉCNICO NACIONAL SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

#### ACTA DE REVISIÓN DE TESIS

| En la Ciu | ıdad de                            | México, D.F.      | siendo la        | s 11:00         | horas del dí    | a 15        | del n   | nes ( | de  |

|-----------|------------------------------------|-------------------|------------------|-----------------|-----------------|-------------|---------|-------|-----|

| noviemb   | re de <u>2012</u> s                | e reunieron los n | niembros de      | la Comisión R   | evisora de la   | Tesis, des  | ignada  | 3     |     |

| por el Co | olegio de Profesor                 | res de Estudios d | le Posgrado      | e Investigación | n del:          |             |         |       |     |

|           |                                    | Centro de         | Investigaci      | ón en Compu     | ıtación         |             |         |       |     |

| para exa  | minar la tesis titu                | lada:             |                  |                 |                 |             |         |       |     |

|           | "Sensor v                          | rirtual con entre | namiento er      | línea implen    | nentado sobr    | e FPGA"     |         |       |     |

| Presentac | da por el alumno:                  |                   |                  |                 |                 |             |         |       |     |

| riescilla | FLORES                             |                   | VELÁZQUEZ        | ,               |                 | SERGIO      |         |       |     |

|           | Apellido paterno                   |                   | Apellido materno |                 |                 | Nombre(s)   |         |       |     |

|           |                                    |                   | (                | Con registro:   | B 1 (           | 0 1         | 8       | 7     | 1   |

| aspirante | de: MAESTRÍA E                     | N CIENCIAS EN I   | NGENIERÍA D      | E CÓMPUTO       | CON OPCIÓN      | EN SISTEM   | /IAS DI | GITA  | LES |

|           | s de intercambi<br>en virtud de qu |                   |                  |                 |                 |             |         |       |     |

|           |                                    | LAC               | OMISIÓN F        | REVISORA        | v.              |             |         |       |     |

|           |                                    |                   | Directores de    | Tesis           | 1               |             |         |       |     |

|           | X                                  | H.                |                  |                 | Appli.          |             |         |       |     |

|           | r. Marco Antonio N                 | Noreno Armendáriz |                  | Dr. C           | arlos Alberto C | ruz Villar  |         |       |     |

|           | La                                 | 2                 |                  |                 | full of         |             | ۷       |       |     |

|           | Dr. Sergio Su                      | árez Guerra       |                  | Dr. Luis F      | astor Sánchez   | z Fernández | Z       |       |     |

|           | M. en C. Osvaldo                   | RESIDENTE DE      | Mallon           | DE PROFESO      | CO NACIONAL     | e Ponce     |         |       |     |

|           |                                    |                   |                  | EN COMPUTA      | CION            |             |         |       |     |

DIRECCION

# INSTITUTO POLITÉCNICO NACIONAL SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

#### CARTA DE CESIÓN DE DERECHOS

En la ciudad de México, el día 12 del mes de noviembre del año 2012, el que suscribe Sergio Flores Velázquez alumno del Programa de Maestría en Ciencias en Ingeniería de Cómputo, opción en Sistemas Digitales, con número de registro B101871, adscrito al Centro de Investigación en Computación, manifiesta que es autor intelectual del presente trabajo de Tesis bajo la dirección del Dr. Marco Antonio Moreno Armendáriz y el Dr. Carlos Alberto Cruz Villar cede los derechos del trabajo titulado "Sensor Virtual con entrenamiento en línea implementado sobre FPGA", al Instituto Politécnico Nacional para su difusión, con fines académicos y de investigación.

Los usuarios de la información no deben reproducir el contenido textual, gráficas o datos del trabajo sin el permiso expreso del autor y/o director del trabajo. Este puede ser obtenido escribiendo a las siguientes direcciones ing.tuzo.biker@gmail.com, mam\_armendariz@cic.ipn.mx y cacruz@cinvestav.mx. Si el permiso se otorga, el usuario deberá dar el agradecimiento correspondiente y citar la fuente del mismo.

Sergio Flores Velázquez

# Resumen

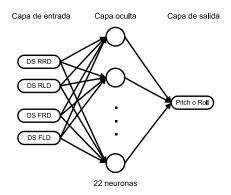

La presente tesis detalla el diseño e implementación un sensor virtual sobre un FPGA. El sensor virtual es del tipo *caja negra* y utiliza como metodología de diseño el aprendizaje de la red neuronal para adaptarse a variaciones que pudiesen presentarse a lo largo de la operación del sistema.

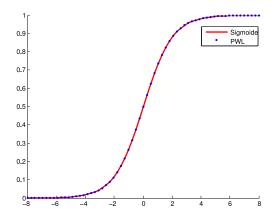

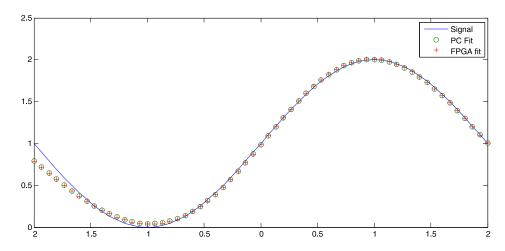

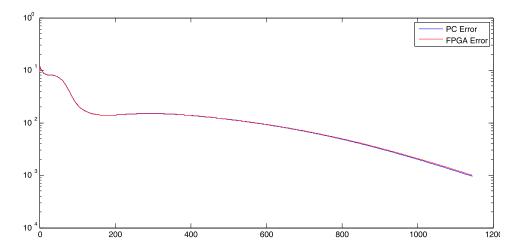

La implementación de la red neuronal comprende dos etapas: la propagación hacia adelante de las entradas y el algoritmo de aprendizaje. Las neuronas de las capas ocultas tienen función de activación sigmoide logarítmica, mientras que las de la capa de salida, la función lineal. La función sigmoide logarítmica se implementó mediante la linealización por partes. La propagación hacia adelante de la red neuronal se puede ejecutar de forma serial, por bloques o bien totalmente paralela, con lo que se consigue un menor tiempo de ejecución a costa de un mayor uso de recursos del FPGA.

El algoritmo de aprendizaje de la red neuronal tiene como finalidad ajustar los valores de los parámetros de la red neuronal, de esta manera se consigue un regresor capaz de ajustarse a una señal no lineal.

Esta implementación resultó tener un alto grado de precisión con un moderado uso de recursos, lo que da pie a su integración en proyectos que puedan ser desarrollados a futuro.

# Abstract

This thesis describes the virtual sensor design and implementation on FPGA. The *black box* virtual sensor was designed using the neural network learning to adapt it to variations that may occur throughout the system operation.

The neural network implementation comprises two stages: the feedforward inputs and the learning algorithm. The hidden layers neurons have the logarithmic sigmoid function as activation function, while the output layer has the linear function. The logarithmic sigmoid function was implemented by using the piecewise linearization. The feedforward neural network can be run serially, blocks or fully parallel, thus result in lower execution time at the cost of increased use of FPGA resources.

The neural network learning algorithm is designed to adjust the neural network parameters to achieving a regressor capable of adjusting itself to a nonlinear signal.

This implementation has a very high degree of accuracy with a moderate use of resources, which leads to their integration in projects that may be developed in the future.

## Agradecimientos

La presente tesis representa la culminación de un gran esfuerzo que no hubiese sido posible sin el apoyo, opiniones, ánimos y paciencia de varias personas.

Agradezco al Dr. Marco Antonio Moreno Armendáriz por su paciencia, apoyo y confianza que depositó en mi persona para la elaboración de este trabajo de tesis. Hubo momentos díficiles, de gran premura, los cuales me hicieron salir adelante y culminar con este documento todo el trabajo desarrollado.

Gracias también a mis compañeros por sus consejos, apoyo y asesorías que me fueron de gran ayuda en la realización de este trabajo. Gracias César por tu ejemplo de constancia, gracias Carlos por tus sugerencias. Gracias Pamela, Alejandro, Jesús, José Luis y Rodolfo por haberme acompañado durante estos casi tres años.

Gracias a todos aquellos amigos quienes me apoyaron durante este tiempo: con una palmada, un abrazo o simplemente, con una frase de ánimo. Quiero agradecerle a Mayra por su apoyo y compañía a lo largo de este tiempo.

Gracias al CONACYT y a la SIP-IPN por el apoyo económico brindado, sin el cual la elaboración de la presente tesis no habría sido posible.

Es momento de agradecer a mi familia: a mis padres Patricia y Sergio por sus palabras de aliento en aquellos momentos difíciles por los que pasé, por siempre estar al pendiente de mi trabajo; gracias por su apoyo incondicional. Gracias a mi hermana Betsabé por esos momentos de risa, enojos y tristezas; a mis abuelos por sus infinitas bendiciones.

Tío: donde sea que estés, sigue rodando... espérame en la cima...

A todos...

Gracias!!!

# Índice general

| Re                 | esum  | en                                  | Ι   |

|--------------------|-------|-------------------------------------|-----|

| $\mathbf{A}$       | bstra | ct                                  | II  |

| $\mathbf{A}_{\xi}$ | grade | ecimientos                          | III |

| $\mathbf{G}$       | losar | io                                  | XI  |

| 1.                 | Intr  | oducción                            | 1   |

|                    | 1.1.  | Antecedentes                        | 2   |

|                    | 1.2.  | Planteamiento del problema          | 4   |

|                    | 1.3.  | Justificación                       | 5   |

|                    | 1.4.  | Hipótesis                           | 5   |

|                    | 1.5.  | Objetivos                           | 5   |

|                    |       | 1.5.1. Objetivo general             | 5   |

|                    |       | 1.5.2. Objetivos específicos        | 5   |

|                    | 1.6.  | Alcances y límites                  | 6   |

|                    | 1.7.  | Contribución                        | 6   |

|                    |       | 1.7.1. Producto de la Investigación | 6   |

|                    | 1.8.  |                                     | 6   |

| 2.                 | Esta  | ado del Arte                        | 8   |

|                    | 2.1.  | Resumen                             | 15  |

| 3. | Maı  | rco Teórico                                      | 16              |

|----|------|--------------------------------------------------|-----------------|

|    | 3.1. | Neurona Biológica                                | 17              |

|    | 3.2. | Neurona Artificial                               | 18              |

|    | 3.3. | Tipos de Redes Neuronales Artificiales           | 21              |

|    |      | 3.3.1. Capas de neuronas                         | 21              |

|    |      | 3.3.2. Redes multicapa                           | 22              |

|    | 3.4. | Perceptrón multicapa                             | 23              |

|    |      | 3.4.1. Arquitectura del Perceptrón multicapa     | 23              |

|    |      | 3.4.2. Propagación hacia adelante                | 24              |

|    | 3.5. | Aprendizaje de la Red Neuronal Artificial        | 24              |

|    |      | 3.5.1. Criterios de Finalización                 | 24              |

|    |      | 3.5.2. Diseño de las Reglas de Aprendizaje       | 26              |

|    |      | 3.5.3. Ecuaciones Generales                      | 31              |

|    |      | 3.5.4. Proceso de aprendizaje                    | 32              |

|    | 3.6. | Resumen                                          | 34              |

| 4. | Des  | arrollo de la Investigación                      | 35              |

|    |      | Panorama General                                 | 36              |

|    | 4.2. |                                                  | 38              |

|    |      | 4.2.1. Módulo <i>Multadder</i>                   | 42              |

|    |      | 4.2.2. Función de activación                     | 43              |

|    |      | 4.2.3. Modos de ejecución                        | 46              |

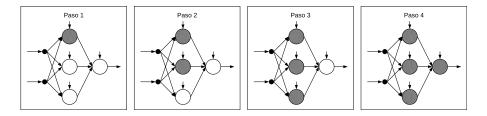

|    |      | 4.2.3.1. Ejecución Serial                        | 46              |

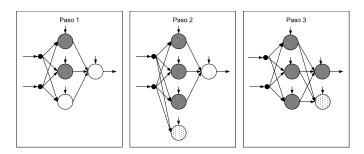

|    |      | 4.2.3.2. Ejecución por bloques                   | 47              |

|    |      | 4.2.3.3. Ejecución en Paralelo                   | 49              |

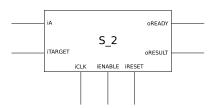

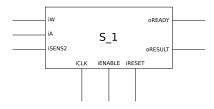

|    | 4.3. | Algoritmo de Aprendizaje                         | 50              |

|    |      | 4.3.1. Cálculo de Sensitividades                 |                 |

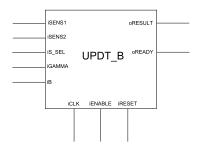

|    |      | 4.3.2. Actualización de bias                     |                 |

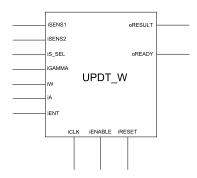

|    |      | 4.3.3. Actualización de pesos sinápticos         |                 |

|    |      | 4.3.4. Actualización de entradas                 |                 |

|    |      | 4.3.5. Cálculo del Error de Iteración $(E_{It})$ |                 |

|    | 4.4. | Comunicación PC-FPGA                             | 57              |

|    | 4.5. |                                                  | 58              |

| 5  | Dno  | sentación de Resultados                          | 59              |

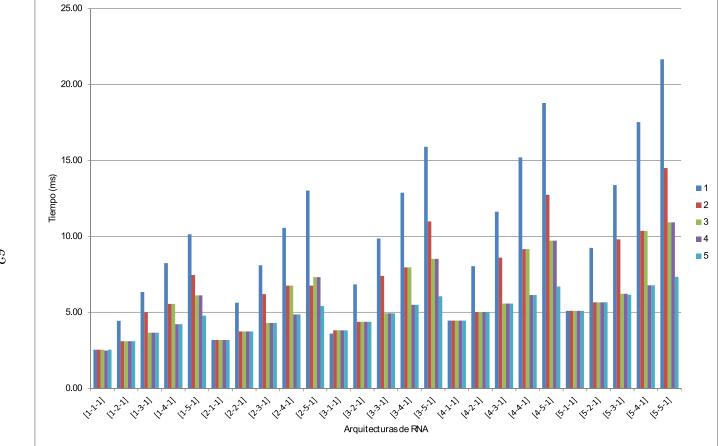

| J. | 5.1. |                                                  | บฮ              |

|    | J.1. | entrada                                          | 59              |

|    |      | 5.1.1. Caso de estudio                           | $\frac{59}{65}$ |

|    |      | J.1.1. Vasu de estadio                           | $-\omega$       |

|    |       | Resumen                      |    |

|----|-------|------------------------------|----|

| 6. | 6.1.  | clusiones Conclusiones       |    |

| Re | efere | ncias                        | 75 |

| Aı | oénd: | ices                         | 81 |

| Α. | Fun   | ción sigmoidal y su derivada | 81 |

| в. | Inte  | rfaz desarrollada en MatLab  | 83 |

# Índice de figuras

| 1.1. | Procedimiento para diseñar un sensor virtual              |

|------|-----------------------------------------------------------|

| 1.2. | Esquema de diseño de un sensor virtual adaptable [1] 4    |

| 2.1. | Referencias por año de publicación                        |

| 2.2. | Referencias por tipo de publicación                       |

| 3.1. | Neurona biológica                                         |

| 3.2. | Neurona artificial con una entrada                        |

| 3.3. | Funciones de activación lineales                          |

| 3.4. | Funciones de activación no lineales                       |

| 3.5. | Neurona artificial con múltiples entradas                 |

| 3.6. | Capa de $S$ neuronas                                      |

| 3.7. | Red neuronal multicapa                                    |

| 3.8. | Perceptrón Multicapa en representación matricial 24       |

| 3.9. |                                                           |

| 4.1. | Tarjeta Altera DE2 70                                     |

| 4.2. | Formato de punto flotante de 32 bits                      |

| 4.3. | Diagrama general de la Red Neuronal y su aprendizaje 37   |

| 4.4. | Máquina de Estados de la propagación hacia adelante de la |

|      | Red Neuronal Artificial                                   |

| 4.5. | Arquitectura general de la propagación hacia adelante 41  |

| 4.6. | Módulo <i>Multadder</i>                                   |

| 4.7. | Linealización de la función sigmoidal                     |

| 4 |

|---|

| 7 |

| 8 |

| 0 |

| 0 |

| 1 |

| 2 |

| 3 |

| 4 |

| 5 |

| 7 |

| 2 |

| 6 |

|   |

| 6 |

| 7 |

| 8 |

| 8 |

| 9 |

| 9 |

|   |

| 1 |

|   |

# Índice de tablas

| 2.1. | Longitudes de datos reportadas                   |

|------|--------------------------------------------------|

| 5.1. | Uso de recursos del FPGA                         |

| 5.2. | Tiempos con diversos modos de ejecución 6        |

| 5.3. | Frecuencias máximas de operación 63              |

| 5.4. | Tiempos de ejecución                             |

| 5.5. | Resultados obtenidos con el FPGA y con MatLab 64 |

| 5.6. | Error promedio de los sensores virtuales         |

# Lista de algoritmos

| 4.1. | Conversión de una neurona simple a multientrada | 42 |

|------|-------------------------------------------------|----|

| 4.2. | Linealización de la función sigmoidal           | 45 |

| 4.3. | Ejecución Serial                                | 47 |

| 4.4. | Ejecución a bloques                             | 48 |

| 4.5. | Ejecución en Paralelo                           | 49 |

| 4.6. | Cálculo de $S^1$                                | 53 |

| 4.7. | Actualización de las entradas                   | 55 |

| 4.8. | Cálculo de $E_{It}$                             | 56 |

# Glosario

#### **CMOS**

Del inglés Complementary Metal Oxide Semiconductor. Tipo de tecnología de semiconductores ampliamente usado. Los semiconductores CMOS utilizan circuitos NMOS (polaridad negativa) y PMOS (polaridad positiva). Dado que sólo un tipo de circuito está activo en un tiempo determinado, los chips CMOS requieren menos energía que los chips que usan sólo un tipo de transistor. 2.0

#### **FPGA**

Del inglés Field Programmable Gate Array, fue inventadas en 1984 por Ross Freeman y Bernard Vonderschmitt, co-fundadores de Xilinx, es un dispositivo semiconductor que contiene bloques de lógica cuya interconexión y funcionalidad se puede programar. La lógica programable puede reproducir desde funciones tan sencillas como las llevadas a cabo por una puerta lógica o un sistema combinacional hasta complejos sistemas en un chip. 1.2, 2.0, 4.0, 5.0

#### $\mathbf{LE}$

Del inglés *Logic Element*. Es la unidad lógica más pequeña en la arquitectura del FPGA(Altera). Como principal característica contiene una tabla de búsqueda (LUT, look-up table) de cuatro entradas, que es un generador de funciones, por lo que puede implementar cualquier función de cuatro variables. 4.0, 5.1

#### LUT

Del inglés Look-Up Table, es una estructura de datos que se usa para substituir la ejecución una rutina mediante el indexado de los registros. Son muy útiles en el ahorro de tiempo y recursos de procesamiento. Un ejemplo práctico de la utilidad de una LUT es su uso para obtener resultados de funciones sin necesidad de hacer el cálculo, utilizando como índice el valor de entrada y como resultado, el valor almacenado en la localidad respectiva. 2.0, 4.2

#### VHDL

Del inglés Very High Speed Integrated Circuit Hardware Description Language, lenguaje creado a partir de un proyecto promovido por el gobierno de Estados Unidos en 1981 y fue homologado por el IEEE en 1987 en el estándar 1076-87. VHDL utiliza una metodología de diseño de arriba abajo (top-bottom) que permite describir el circuito de forma estructural (señales y sus conexiones) y funcional (qué hace). Cada bloque se puede definir empleando subcircuitos definidos en el mismo proyecto o disponibles en librerías propias o de terceros. 1.4

# Introducción

Los sensores virtuales representan una herramienta que permite la estimación de variables cuyo proceso de medición presenta dificultades técnicas, o inclusive no es posible realizar dado que no se disponen de los sensores físicos necesarios. Su uso se extiende al control y/o seguridad de procesos, o bien, simplemente en tareas de monitoreo. Los sensores virtuales también conocidos como sensores suaves ya que son una combinación entre los conceptos software y sensor. El concepto software se refiere a que utilizan modelos computacionales en su operación, mientras que sensor se debe a que entrega información similar a un sensor físico [2].

La industria química ha encontrado en los sensores virtuales una alternativa para la estimación en línea de variables como la concentración de elementos químicos, ya que estas mediciones tardan alrededor de 30 minutos en estar listas. Otros ejemplos de industrias que se ha beneficiado del uso de los sensores virtuales es la industria minera y la automotriz.

#### 1.1. Antecedentes

Los sensores virtuales están basados en un modelo que representa la dinámica del sistema, este modelo relaciona las entradas del sensor (señales medidas) y las señales deseadas. Conforme al trabajo de Jassar [3], existen tres principales metodologías para el diseño de sensores virtuales:

- ▶ Modelado matemático del sistema físico

- ▶ Redes neuronales artificiales

- ▶ Lógica difusa

De acuerdo a su principio de operación, se puede clasificar a los sensores virtuales en dos categorías [4]:

- ▶ Manejados por modelo: esos sensores conocidos como modelos de caja blanca se basan en la descripción mediante ecuaciones matemáticas los principios del proceso químico o físico. Aunque los modelos reflejan claramente el mecanismo de operación, su desarrollo requiere un profundo entendimiento y conocimiento del proceso, lo que resulta complicado em un proceso real.

- ▶ Manejados por datos: conocidos como modelos de caja negra se construyen a partir de observaciones empíricas del proceso, sin ningún tipo de información del proceso interno.

Algunos ejemplos de sensores virtuales manejados por datos son sensores basados en el filtro de Kalman extendido [5], o en observadores de estado [6], esta familia de sensores virtuales se basa en el modelo de los principios del sistema del cual se desea estimar las variables. Estos modelos fundamentados en leyes físicas que rigen el sistema son desarrollados y utlizados para diseño y control de sistemas, por ello se enfocan en los estados ideales del sistema, lo cual es un gran inconveniente para su operación en ambientes reales. Por ello, los sensores manejados por datos obtenidos de la operación del sistema en entornos no controlados han incrementado su uso.

Entre las técnicas empleadas para el diseño de sensores virtuales manejados por datos, se encuentran el análisis de componentes principales [7], su combinación con modelos de regresión [8], mínimos cuadrados parciales [9], redes neuronales artificiales [10], sistemas neurodifusos [11] y máquinas de soporte vectorial [12]. Las aplicaciones más comunes de los sensores virtuales se encuentran en monitoreo en línea [13], control en lazo cerrado con bajos periodos de muestreo [14] y detección de fallas [15].

Los sensores virtuales son exitosos en pruebas en periodos cortos, sin embargo, con su uso en periodos prolongados de tiempo, se observó que las estimaciones empiezan a tener diferencias sustanciales con las mediciones reales del proceso obtenidas en laboratorios, esto debido a cambios clim'aticos, cambios en propiedades de fuentes de alimentación, entre otros factores, es decir, las condiciones con las que los sensores fueron entrenados cambiaron con el paso del tiempo con respecto a las condiciones de operación actuales. Esto dió origen al desarrollo de sensores virtuales adaptables, que son capaces de lidiar con las variaciones del entorno en el que fueron entrenados.

Los métodos de aprendizaje más comunes en sensores virtuales adaptables son técnicas de ventanas móviles, técnicas de adaptación recursiva y métodos basados en conjuntos [16].

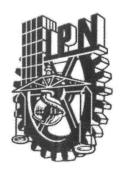

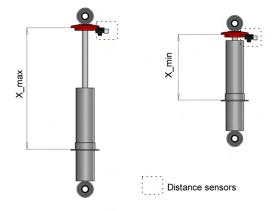

Fortuna [17] propone la siguiente metodología para el diseño de sensores virtuales (ver figura 1.1).

Figura 1.1: Procedimiento para diseñar un sensor virtual.

Como primer paso del diseño se seleccionan los datos medibles del sistema para obtener la salida deseada. Esto se puede realizar de diferentes maneras, pero es vital seleccionar aquellas variables que estén directamente relacionadas con el fenómeno.

Una vez que se han identificado las señales a medir, es necesario determinar qué sensores serán utilizados para dichas mediciones. Algunas veces

es necesario agregar una capa de filtrado para eliminar posibles ruidos del ambiente o del mismo sistema.

Posteriormente, se plantea el modelo que relaciona las señales medidas con las señales a estimar. La validación del modelo consiste en hacer estimaciones de señales que no se hayan incluído en su diseño, y finalmente, se comparan las señales obtenidas con las esperadas.

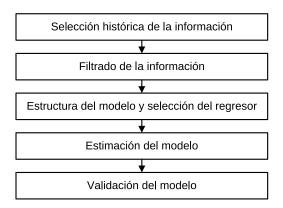

A diferencia del trabajo de Fortuna [17], el trabajo realizado por Ma [1] presenta una nueva metodología para la creación de un sensor virtual adaptable, dicha metodología se muestra en la figura 1.2.

Figura 1.2: Esquema de diseño de un sensor virtual adaptable [1].

## 1.2. Planteamiento del problema

Actualmente existen algunos sistemas que presentan dificultades técnicas en el proceso de medición de algunas variables de gran importancia. Tales dificultades pueden ser que no se pueden localizar los sensores físicos en el lugar adecuado o bien, que la medición presenta graves retrasos, sin embargo

se dispone de información que se puede correlacionar y con esto determinar el comportamiento estas variables no medibles directamente. Para ello, una de las estrategias más comunes es el uso de sensores virtuales, los cuales permiten reducir costos o realizar un diagnostico rápido del funcionamiento del sistema.

### 1.3. Justificación

La implementación de una red neuronal con entrenamiento en línea en hardware se puede integrar como un sensor virtual para la estimación de valores cuyas mediciones de sistemas reales no se puedan realizar. La implementación en hardware le da al sensor una mayor rapidez además de posibilitar su integración en proyectos a futuro.

## 1.4. Hipótesis

El sensor virtual implementado en este trabajo será ser capaz de adaptarse a variaciones en las señales no lineales que recibe como entrada para obtener un resultado a la salida con el que se puedan estimar mediciones de variables en sistemas reales.

## 1.5. Objetivos

#### 1.5.1. Objetivo general

Este trabajo tiene como objetivo la implementación de un sensor virtual con entrenamiento en línea para estimar mediciones de variables dentro de sistemas reales que no sean posibles de medir directamente. La estimación se realizará mediante información de variables dentro del sistema que sí se pueden medir.

## 1.5.2. Objetivos específicos

▶ Revisar el estado del arte referente a la implementación de sensores virtuales basados en redes neuronales.

- ⊳ Implementar sobre un FPGA un perceptrón multicapa junto con la regla de aprendizaje backpropagation.

- Validar el desempeño del sistema mediante la aproximación de señales no lineales.

## 1.6. Alcances y límites

En este trabajo se busca implementar un sensor virtual adaptable basado en el aprendizaje de un Perceptrón multicapa. La arquitectura de la red neuronal será de tres capas: capa de entrada, una capa oculta y la capa de salida. En teoría, la capa oculta puede tener cualquier cantidad de neuronas; pero en la práctica no es así, está limitada por el tamaño de la memoria en la que se almacenan los pesos sinápticos, un incremento en el tamaño de la memoria puede dar como resultado un consumo excesivo de recursos.

#### 1.7. Contribución

Mediante el desarrollo de esta tesis se implementará un Perceptrón multicapa junto con sus algoritmo de aprendizaje sobre un FPGA en el cual se actualizarán los pesos sinápticos y umbrales de manera automática. Esta implementación será utilizada como un sensor virtual.

## 1.7.1. Producto de la Investigación

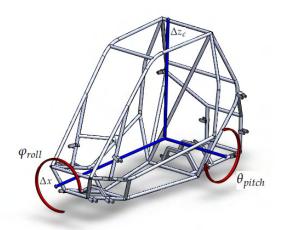

Se logró la publicación de un artículo en el congreso IASTED International Conference on Signal and Image Processing (SIP 2012) [18]:

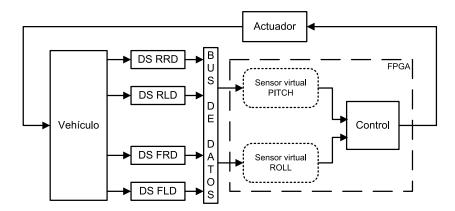

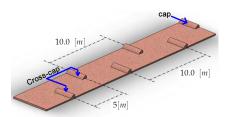

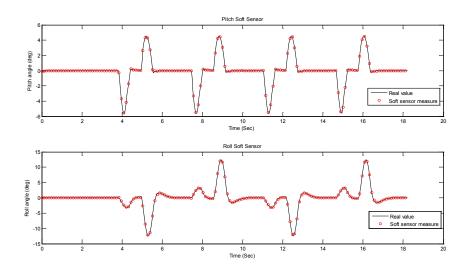

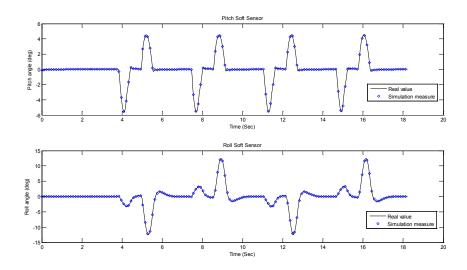

Marco A. Moreno-Armendáriz, Carlos A. Duchanoy, Sergio Flores-Velázquez, Carlos A. Cruz-Villar. (2012). FPGA Implementation of a Pitch and Roll Soft Sensors for Active Suspension System. Proceedings of the IASTED International Conference Signal and Image Processing (SIP 2012) pp 99-106.

## 1.8. Organización de la tesis

Capítulo 1 Presenta al lector una introducción a los sensores virtuales. Asimismo establece de manera clara la problemática a resolver, plantea los

- objetivos, los alcances y las limitaciones del trabajo por realizar.

- Capítulo 2 Ofrece una semblanza del estado del arte referente a la implementación sensores virtuales y redes neuronales artificiales sobre FPGAs. Aquí se describen diversas arquitecturas utilizadas para el diseño de sensores virtuales, así como de redes neuronales artificiales.

- Capítulo 3 Expone a profundidad los fundamentos teóricos que tienen como base tanto las redes neuronales artificiales como el algoritmo de aprendizaje basado en la propagación hacia atrás del error y los criterios que marcan el final del entrenamiento de las redes neuronales.

- Capítulo 4 Contiene la parte medular de esta tesis, ya que a lo largo de este capítulo se describe el desarrollo de la implementación de la red neuronal artificial y del algoritmo de aprendizaje *Backpropagation* en el FPGA. Este capítulo contiene esquemas y algoritmos que ejemplifican todos aquellos procesos que están inmersos en la ejecución y aprendizaje de redes neuronales.

- Capítulo 5 Muestra los resultados obtenidos mediante la ejecución de las etapas de las que se conforma el proyecto, así como se realiza una comparativa entre este trabajo y una aplicación desarrollada en un paquete de cálculo, para ello se incluyen gráficos y tablas que ayudan al lector a comprender dichos resultados.

- Capítulo 6 Entrega las conclusiones dados los objetivos alcanzados y posibles opciones de trabajo para nuevos desarrollos no solo en en el campo de las redes neuronales, sino como su integración como un componente en un probable proyecto a futuro.

- **Apéndices** Incluyen la manera de obtener la derivada de la función sigmoide logarítmica. Aquí también se presentan códigos fuente en MatLab y VHDL que fueron utilizados en el desarrollo de esta tesis.

# Estado del Arte

Los sensores virtuales son ampliamente utilizados en casos donde las tareas de medición son difíciles de llevar a cabo. Existen algunos casos en los que la medición tiene retrasos de tiempo considerables. Los valores de interés son calculados de forma indirecta a partir de datos cuyas mediciones son más fáciles de obtener. En estos sensores, el uso de redes neuronales es un enfoque muy exitoso en el análisis de datos con mucho ruido, o bien en variables no lineales [19].

La industria minera ha utilizado a los sensores virtuales para determinar partículas de minerales a partir de imágenes; esto provee una herramienta muy valiosa para administrar los procesos de la minería de una mejor manera. El modelado mediante redes neuronales brinda resultados precisos en la estimación del tamaño de partículas de minerales [20].

La industria química también se ha beneficiado del uso de redes neuronales dentro de sensores virtuales. Una de sus aplicaciones corresponde a la detección de óxidos de Nitrógeno  $(NO_x)$  y Ozono  $(O_2)$  en calentadores industriales. En este caso se colocaron sensores físicos en las tuberías para monitorear su sobrecalentamiento, algunos otros sensores se colocaron en las entradas de combustible y de oxígeno a la cámara de combustión para medir la mezcla que se consume. La red neuronal determina la cantidad de contaminantes que son expedidos a la atmósfera [21].

Otra aplicación de los sensores virtuales dentro de la industria química se

utiliza para estimar el punto de congelamiento del queroseno proveniente del proceso de destilación del petróleo crudo. La característica más importante en este trabajo es el reducido conjunto de datos. El uso de máquinas de soporte vectorial (SVM) ayudó a los autores a conseguir una buena precisión en el aprendizaje para este caso, sin embargo, la generalización de la red neuronal mejora con la introducción de ruido a las muestras de entrenamiento [22].

Actualmente las redes neuronales artificiales constituyen una herramienta ampliamente utilizada para resolver una amplia gama de problemas. Debido a esta variedad, también existen distintos enfoques para su integración al problema que se desea resolver. Los avances tecnológicos que existen hoy en día incluyen diversos dispositivos que pueden ser empleados para implementar redes neuronales en hardware, sin nembargo, los FPGAs resultan ser una excelente solución para ello. Una de las mayores ventajas del uso de esta tecnología radica en su capacidad de ejecutar tareas de forma paralela, por otra parte, también destacan su velocidad de operación y la sencillez con la que el diseño se puede ser modificado inclusive en tiempo de ejecución (reconfiguración). Sin embargo, pueden ser implementadas también mediante circuitos analógicos (CMOS), estas implementaciones explotan el carácter no lineal de las redes neuronales, además de ser más rápidas y consumir menor cantidad de energía; pero se ven afectados por ruido, calor y su procesamiento no resulta ser muy exacto [23].

Las redes neuronales artificiales que se implementan en FPGA que poseen la capacidad de ser entrenadas, se pueden clasificar en dos tipos:

- ⊳ Entrenamiento *On-Line*: el algoritmo de aprendizaje de la red neuronal se implementa en el dispositivo con lo que se logra un entrenamiento continuo a costa de un mayor consumo de recursos de hardware. [23]

- ▷ Entrenamiento Offline: consiste en obtener los valores de los pesos sinápticos y umbrales mediante una aplicación desarrollada en software. La red neuronal trabaja con los parámetros fijos a lo largo de su ejecución. [24, 25]

Existen trabajos que se valen de la capacidad de reconfiguración de las redes neuronales para trabajar en paralelo las tareas de aprendizaje de la red neuronal artificial. El proyecto Run-TIME Reconfiguration Artificial Neural

Network (RRANN) justamente aplica ese principio. Esta arquitectura divide la ejecución del algoritmo *backpropagation* en tres etapas que se ejecutan secuencialmente:

- ▶ Propagación hacia adelante: toma las entradas y las propaga a lo largo de la red para obtener una salida de la red.

- ▶ Propagación hacia atrás: toma el valor de salida de la red y obtiene el error de la salida y lo propaga hacia atrás para obtener el error de cada neurona de las capas ocultas.

- ▶ Actualización: se aplican las reglas de aprendizaje para obtener los nuevos valores de los pesos sinápticos.

El fin de la etapa de actualización, marca la terminación del cálculo de patrón de entrenamiento. Este proceso se repite para todos los patrones hasta que la red esté suficientemente entrenada.

RRANN utiliza un FPGA con múltiples procesadores neuronales, cada uno de los cuales contiene 6 neuronas en hardware cuyas subrutinas y memoria RAM son controladas por una máquina de estados. Los procesadores siguen las instrucciones de un controlador global. La RAM de cada procesador almacena los pesos y los resultados deseados, además de actuar como buffer para los valores de error. Para utilizar menor cantidad de recursos, se emplean tablas LUT para implementar las funciones de activación y sus respectivas derivadas.

La reconfiguración en tiempo de ejecución le da al usuario tres maneras de implementar la arquitectura.

- 1. Configura las tres etapas de operación en el FPGA para la ejecución totalmente en paralelo.

- 2. Configura la propagación hacia adelante y la actualización en el FPGA, mientras que el FPGA se reconfigura cuando se ejecuta la retropropagación.

- 3. Configura solamente una de las tres etapas en el FPGA, de manera que al finalizar la ejecución de una, se reconfigura la siguiente etapa.

La tercer etapa es la única en ser diseñada, implementada y probada. El proyecto fue implementado en una tarjeta National Technology Inc. que incluye un FPGA, las neuronas en hardware se implementaron en un FPGA Xilinx XC3090, ya que se valen de una técnica de reconfiguración en tiempo de ejecución. Los autores estiman que podría funcionar sobre los 40 MHz, aunque fue operado a una frecuencia de 14 MHz [26].

Algunas implementaciones de redes neuronales sobre FPGAs tienen como principal premisa un mínimo uso de recursos disponibles, sacrificando en cierto grado el niver de precisión y la velocidad de procesamiento. Aunque también es importante destacar que la función de activación utilizada en las neuronas de la red neuronal determina en gran parte el consumo total de recursos, por ello se vuelve indispensable el uso de algoritmos de aproximación a las funciones no lineales (tangente sigmoidal, sigmoide logarítmica, entre otras), entre los que destacan la linealización y el uso de tablas LUT [27, 28].

Savran y Ünsal [29] resuelven el problema de la XOR con 3 entradas mediante el uso de una red neuronal [3-5-1]. La red neuronal que es controlada por una máquina de estados que alimenta a las neuronas de la red. Cada neurona está compuesta por los siguientes elementos:

- ▶ Un multiplicador de 8 bits en la entradas y 16 en la salida.

- ▶ Una memoria ROM para almacenar los pesos.

- ▶ Un acumulador de 16 bits.

Los autores utilizaron una función de activación por capa ya que, debido al carácter serial de esta implementación, cada ciclo de reloj existe un resultado válido del acumulador. Es decir, para ejecutar una capa de 3 neuronas, es necesario que transcurran 3 ciclos de reloj para tener los resultados de las neuronas listas, aunque éstas se procesan en paralelo. Los resultados de las funciones de activación se calculan en MatLab y se vacían en archivos para inicializar memorias ROM en el FPGA Xilinx Spartan II. La red neuronal requiere de 20 ciclos de reloj para ser procesada completamente.

Sahin, Becerikli y Yazici [30] implementaron un modelo de red neuronal [2-3-1] en un FPGA Xilinx Spartan IIE. Utilizaron aritmética de punto flotante de 32 bits. Diseñaron un módulo de multiplicación y uno de suma en punto

flotante, los cuales utilizan la mayor cantidad de recursos del FPGA. Utilizan datos de 32 bits ya que determinaron que este ancho de datos mantiene un equilibrio entre los recursos utilizados y el tiempo requerido para realizar el cálculo de la red, ya que para minimizar los recursos se pudiesen utilizar datos de 8 bits, pero entonces la red no serviría para su uso como controlador de tiempo real. En esta estructura tienen un multiplicador y un sumador por capa, las salidas de una capa entran de manera paralela a la siguiente capa, mientras que los pesos lo hacen serialmente a los multiplicadores. Los resultados de la multiplicación se almacenan en la memoria ROM de cada neurona, estos resultados entran de forma serial al sumador, su resultado entra a una LUT. La función de activación es una sigmoide con un intervalo de -10 a 2 con pasos de 0,2. Debido a la estructura que fue implementada, solo una neurona, únicamente necesitan un multiplicador y un sumador, además de una tabla para almacenar los resultados de la función para cada neurona, cuya ejecución se repite tantas veces como neuronas existan en la red. En el artículo, los autores reportan un error de 0.059323 al calcular la red en el FPGA con respecto a una implementación en software (2.3274321322 en software contra 2.268109 en el FPGA) con entradas  $g_1 = 0.5$  y  $g_2 = -0.25$ .

Otro modelo de red neuronal artificial implementado en FPGA es el propuesto por Himavathi, Anitha, y Muthuramalingam [31], éste se basa en el multiplexado de las capas, es decir sólo se tiene una capa en hardware, la cual tiene tantas neuronas como la capa que más neuronas tenga en la red.

Las neuronas se integran de los siguientes módulos:

- ▷ MUL8: módulo multiplicador de números de 8 bits con signo

- $\triangleright ADD$ : módulo sumador de dos números

- > SIGMA: mdulo que obtiene la sumatoria de los productos de los pesos por las entradas y el umbral

- ▷ SIGMA\_CTRL: unidad de control del procesamiento de la neurona, se encarga de obtener la sumatoria de todos los productos de los pesos por las entradas y el umbral de cada neurona

- ▷ LUT: es el módulo que devuelve el resultado de la función sigmoidal de acuerdo a la salida del módulo SIGMA

Con este modelo, una neurona puede tener 16 entradas sin presentar sobreflujo, aunque incrementando el ancho de palabra, se puede tener capacidad para un mayor número de entradas (en aplicaciones de tiempo real, raramente se excenden 16 entradas). Los datos tienen diferentes longitudes dependiendo de su funció, como se aprecia en Tabla 2.1.

|                                    |        | Parte                 | Parte  |  |

|------------------------------------|--------|-----------------------|--------|--|

| Tipo de Dato                       | Signo  | Entera   Fraccionaria |        |  |

|                                    | (bits) | (bits)                | (bits) |  |

| Entradas                           | 1      | 8                     |        |  |

| Pesos                              | 1      | 8                     | 8      |  |

| Umbrales                           | 1      | 8                     | 16     |  |

| Producto Pesos-Entradas            | 1      | 24                    |        |  |

| Resultado de Sumatoria             | 1      | 12                    | 16     |  |

| Salida de la función de activación | 1      |                       | 8      |  |

Tabla 2.1: Longitud de datos utilizados en el modelo de la red neuronal artificial.

Este trabajo presenta una comparativa entre una neurona con función implementada en una LUT y una neurona con el cálculo de la función mediante la ecuación sigmoidal. Se obtuvo un ahorro de casi el 70 % de recursos mediante la LUT y un ahorro de casi 80 % en tiempo de ejecución.

Otra propuesta en cuanto a la implementación de redes neuronales artificiales en FPGAs es el trabajo de Maeda y Tada [32]. La propuesta se refiere al uso del Método de perturbación simultánea. La ventaja de este método con respecto al backpropagation radica en su simplicidad, ya que puede estimar el gradiente solamente con el uso de los valores de la función del error. En un experimento que reportan, se resuelve el problema de la XOR mediante una red [2-2-1] con un uso del FPGA del 24% (60 000 compuertas de las 250 000 disponibles). La ejecución de la red neuronal inicia con la asignación aleatoria de los pesos sinápticos en el rango de [-255,+255] y una razón de cambio de  $\alpha = 1,25$ .

El trabajo realizado durante este semestre es capaz de resolver cualquier red neuronal, siempre y cuando está dentro de los límites de los recursos del FPGA, por lo que a diferencia del trabajo realizado por Savran y Ünsal [29], resulta una aplicación genérica. Una diferencia notable entre los artículos

anteriormente expuestos consiste en el hecho que se utilizaron LUTs para obtener el resultado de la función de activación (reduciendo de esta manera el tiempo de cálculo), mientras que este modelo linealiza la función almacenando en tablas solamente dos valores que serán procesados para obtener el resultado correcto. Esto hace más lento el procesamiento en general, pero a su vez disminuye de manera considerable la cantidad de recursos de memoria empleados.

A pesar de la existencia de distintas estrategias para implementar redes neuronales en FPGAs, su éxito depende de la implementación eficiente de una simple neurona. Los FPGAs son adecuados para albergar redes neuronales artificiales no solamente por el hecho de ofrecer cálculo en paralelo, sino que también pueden ser reprogramados fácilmente con la finalidad de modificar el diseño sin importar la magnitud de estos cambios [33].

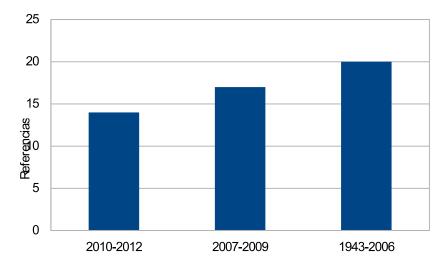

En la figura 2.1 se muestra la cantidad de artículos publicados por año que son citados en esta tesis. Se observa que desde el año 1943 cuando Mc-Culloch y Pitts [34] propusieron el primer modelo de neurona artificial hasta el 2006, se produjeron 20 artículos, sin embargo entre los años 2007 y 2009 se realizaron 17, y desde el 2010 hasta el presente año con el artículo de sensores virtuales de Galicia [9], se han publicado 14 artículos.

Figura 2.1: Referencias por año de publicación.

#### 2.1. Resumen

A lo largo de este capítulo se hace mención de los trabajos previos que se han realizado en el campo de los sensores virtuales, donde se pone de manifiesto la diversidad de aplicaciones en las que pueden ser implementados con éxito. Los sensores virtuales reportados utilizan como base las redes neuronales artificiales, por ello también se incluyen trabajos de implementación en hardware de Redes Neuronales Artificiales. Los resultados reportados son muy variados, en algunos la precisión es el aspecto primordial mientras que en algunos otros lo importante es reducir al mínimo el uso de las unidades lógicas del dispositivo.

Otro aspecto importante de los trabajos es la implementación del algortimo *Backpropagation*, ya que se proponen arquitecturas muy diversas: múltiples FPGAs controlados por un microprocesador, reconfigración de módulos dentro del FPGA dependiendo de la etapa del proceso a ejecutar, entre otros.

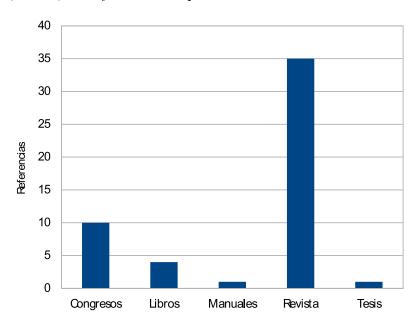

Con el objetivo de resaltar la investigación realizada a lo largo de esta tesis, el siguiente gráfico muestra la cantidad de artículos de revistas científicas, congresos, libros, tesis y manuales que fueron referenciados.

Figura 2.2: Referencias por tipo de publicación.

# Marco Teórico

Las neuronas artificiales imitan el funcionamiento de las células neuronales biológicas que constituyen el cerebro de los seres vivos. Una red neuronal es un arreglo de neuronas dispuestas en capas interconectadas entre sí. Una red neuronal se compone, generalmente de tres capas: capa de entrada, capa oculta y capa de salida; aunque existen algunas aplicaciones que únicamente requieren el uso de la capa de entrada y la capa de salida.

La estructura de una neurona artificial es un modelo de la célula biológica, que se compone de entradas, sumatoria y una función de activación: ya sea la función lineal (utilizada en la capa de salida) o bien alguna función no lineal, ya sea la sigmoidal o la tangente hiperbólica, la cual se emplea frecuentemente en aplicaciones de clasificación.

Debido al carácter cognitivo de las redes neuronales arficiales, una de sus aplicaciones más extendidas es en la aproximación de señales no lineales. Esto se realiza mediante algoritmos de aprendizaje, en los que se ajustan iterativamente los pesos sinápticos y los umbrales de las neuronas para obtener los resultados esperados minimizando así el error de salida.

## 3.1. Neurona Biológica

El desarrollo de la teoría de las Redes Neuronales Artificiales comienza en 1943 cuando el neurobiólogo Walter Pitts y el matemático Warren McCulloch proponen en conjunto el primer modelo de la neurona artificial [34]. Posteriormente en 1958, Frank Rosenblatt desarrolla el *Perceptrón*, que consta de dos capas y es capaz de procesar la información en paralelo [35, 36].

En 1986 se agrega una capa oculta al Perceptrón con la finalidad de entrenar la red para resolver tareas más complejas de clasificación, a este nuevo modelo se le conoce en inglés como Feed-Forward Back-Propagation Neural Network [37]. El algoritmo de aprendizaje que fue presentado por McLelland y Rumelhart es el más ampliamente utilizado a pesar de que han surgido más reglas de aprendizaje.

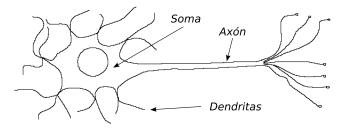

La neurona artificial brinda un modelo matemático de la neurona biológica. Para comprender dicho modelo, la neurona biológica se muestra gráficamente en su forma general en la figura 3.1.

Figura 3.1: Modelo de la neurona biológica.

La neurona se compone de las partes básicas:

- ⊳ Soma es el lugar donde se llevan a cabo las funciones de procesamiento de los estímulos recibidos, también es dónde se realiza la síntesis de proteínas.

- $\triangleright Ax\delta n$  es un nervio en el cual la señal transmitida por el Soma se convierte en impulsos nerviosos que serán propagados a otras células.

- ▶ Dendritas son fibras ramificadas conectadas al Soma que reciben información mediante la Sinápsis.

▷ Sinápsis son las terminales de los axones que se conectan a otras neuronas. Debido a la naturaleza inhibitoria o excitatoria de la sinápsis, es posible atenuar o incrementar el nivel de excitación de la neurona.

#### 3.2. Neurona Artificial

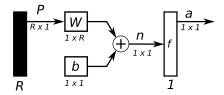

La neurona artificial es una representación simplificada de la neurona biológica, cuyos procesos son tan complejos que actualmente no se conocen en su totalidad. Dicha representación es flexible con la finalidad de adaptarse a la función en la que se vaya a emplear [34].

Una red neuronal es una estructura que procesa información de forma paralela y distribuida, que consta de elementos de procesamiento interconectados entre sí, cada elemento tiene una memoria interna y procesa las senales que recibe del exterior. Cada elemento tiene una salida que se ramifica en tantas conexiones como el problema a resolver lo requiera. La señal de salida del elemento puede ser de cualquier tipo matemático deseado. Todo el procesamiento que ocurre dentro de cada elemento debe ser completamente local: depende únicamente de los valores actuales de las señales de entrada llegan a la elemento a través de conexiones que inciden y en los valores almacenados en la memoria local del elemento de procesamiento [38].

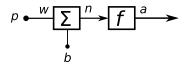

Las neuronas artificiales imitan el funcionamiento del modelo de la neurona biológica presente en el cerebro de los seres vivos. Una neurona artificial de una sola entrada, como la que aparece en la figura 3.2 se puede relacionar fácilmente con una neurona biológica (figura 3.1): el peso sináptico (w) es la fuerza de la sinápsis, el cuerpo de la neurona es la sumatoria  $(\Sigma)$  y la función de activación (f), mientras que la salida (a) es la señal en el axón [39].

Figura 3.2: Neurona artificial con una entrada.

La salida de la neurona de una entrada se caracteriza en la siguiente ecuación:

$$n = f(wp + b)$$

$$a = f(n)$$

(3.1)

#### Función de Activación

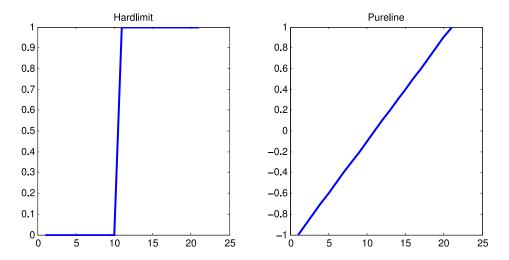

La función f(n) corresponde a la función de activación usada en la neurona. Éstas funciones pueden ser lineales o bien, no lineales dependiendo del uso en el que se vaya a utilizar la red neuronal. Las principales funciones de activación son las siguientes:

- ▶ Funciones Lineales

- Lineal (pureline)

$$f(n) = n (3.2)$$

• Escalón (hardlimit)

$$f(n) = \begin{cases} 0 : n < 0 \\ 1 : n \ge 1 \end{cases}$$

(3.3)

Figura 3.3: Funciones de activación lineales.

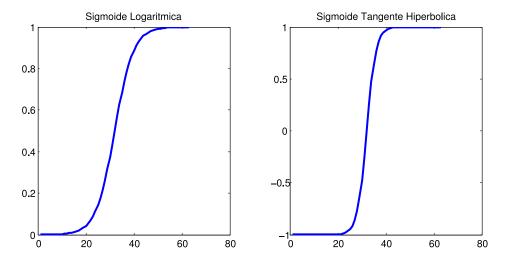

#### ▶ Funciones No Lineales

• Sigmoide logarítmica (logsig)

$$f(n) = \frac{1}{1 + e^{-n}} \tag{3.4}$$

• Sigmoide Tangente Hiperbólica (tansig)

$$f(n) = \frac{e^n - e^{-n}}{e^n + e^{-n}} \tag{3.5}$$

Figura 3.4: Funciones de activación no lineales.

Las funciones lineales se emplean para redes neuronales del tipo ADALI-NE por su sencillez, mientras que la función sigmoidal logarítmica es de uso mayoritariamente en redes neuronales multicapa entrenadas con el algoritmo backpropagation. La función Tangente hiperbólica sigmoidal es muy utilizada en redes multicapa para tareas de clasificación.

#### Neurona de múltiples entradas

Es muy común que una neurona artificial posea múltiples entradas, con pesos sinápticos y un bias, mientras a que a la salida tiene una función de activación f(x).

Figura 3.5: Neurona artificial con múltiples entradas.

El procesamiento de la neurona comienza con la suma de las entradas multiplicadas por sus pesos sinápticos respectivos más el bias:

$$n = \sum_{i=1}^{n} w_i \cdot p_i + b$$

donde  $w_i \cdot p_i$  es la iésima conexión y b es el bias, mientras que la salida de la neurona se representa como:

$$a = f(n)$$

## 3.3. Tipos de Redes Neuronales Artificiales

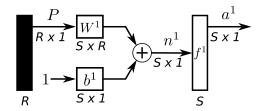

Muchos de los problemas existentes no se pueden resolver aún con una neurona con muchas entradas, de aquí surgió la necesidad de disponer de un conjunto de neuronas, que al trabajar en paralelo forman una *capa*.

## 3.3.1. Capas de neuronas

Una red neuronal de una capa con R entradas y S neuronas se muestra en la figura 3.6. Cada entrada p está conectada a todas las neuronas con un peso w, toda neurona tiene un bias b, un sumador  $\sum$ , una función de activación  $f^1$  y una salida a. Las neuronas dentro de una misma capa pueden tener diferentes funciones de activación.

Figura 3.6: Capa de S neuronas.

## 3.3.2. Redes multicapa

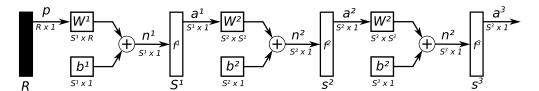

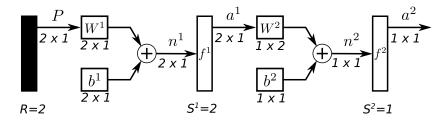

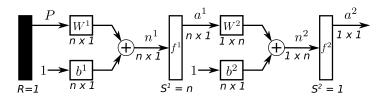

Una red neuronal multicapa como la figura 3.7 agrega complejidad al desarrollo de la misma ya que cada capa tiene sus propios pesos sinápticos y sus bias. Estos parámetros que se agregan en una red multicapa se referencían mediante el superíndice que aparece en cada uno de los elementos, de esta manera se puede tener una red con R entradas,  $S^1$  neuronas en su primer capa y  $S^2$  neuronas en su segunda capa, aunque cada capa puede tener distinta cantidad de neuronas.

Figura 3.7: Red neuronal multicapa.

Como se puede observar en la figura 3.7, las salidas de la primer capa se convierten en las entradas a la segunda capa.

La capa que arroja los resultados de la red se conoce como capa de salida y las capas existentes entre las entradas y la capa de salida son capas ocultas.

Una gran ventaja de las redes neuronales multicapa frente a las redes de solo una capa radica en su poder: una red de dos capas con función de activación sigmoidal en su capa oculta y función lineal en la capa de salida puede ser entrenada para aproximar señales con un buen nivel de certeza, mientras que las redes de una sola capa no pueden hacer esto.

El diseño de una red neuronal puede llegar a ser problemático en sí, aunque pudiesen presentarse situaciones que ayuden en este punto: el número de entradas y salidas de la red depende enteramente de las especificaciones del problema a resolver y el tipo de la señal de salida también puede ayudar

a que función de activación utilizar. La arquitectura de una red de una capa está dada casi en su totalidad por el entorno, mientras que para una red multicapa se vuelve una tarea mucho más compleja. En una red multicapa, no es posible obtener la cantidad de neuronas de la capa oculta del exterior, aunque existen métodos para predecir este número.

# 3.4. Perceptrón multicapa

El modelo del Preceptrón multicapa (MLP, siglas en inglés de *Multilayer Perceptron*) es un aproximador universal, es decir, cualquier función continua puede ser aproximada con un Perceptrón multicapa, con al menos una capa oculta. Esta capacidad ha hecho del Perceptrón multicapa una de las herramientas más utilizadas para la solución de diversos problemas: clasificación y reconocimiento de patrones, control de procesos, modelado de sistemas, predicción de series, entre otros.

El hecho que el Perceptrón multicapa sea ampliamente utilizado, no quiere decir que sea una de las redes más potentes, entre las limitaciones que presenta destaca su largo proceso de aprendizaje en problemas muy complejos, por otra parte, muchas veces resulta muy complicado asignar valores numéricos a las variables del entorno.

# 3.4.1. Arquitectura del Perceptrón multicapa

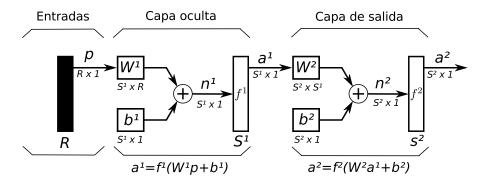

Perceptrón multicapa se compone de tres tipos de capas: entradas, capas ocultas y capa de salida (ver figura 3.8). Esta arquitectura es una cascada de capas de neuronas artificiales. Las entradas ingresan las señales a la red, mientras que a capa de salida envía el resultado del procesamiento de los realizado por las neuronas de las capas ocultas. La estructura de un Perceptrón multicapa se suele representar con el número de entradas, seguido del número de neuronas de cada capa:

$$R - S^1 - S^2 - S^3$$

Las conexiones en el Perceptrón siempre van dirigidas hacia adelante, por lo que se le conoce como red "feedforward" y por lo general cada una de las neuronas de una capa están conectadas a todas las neuronas de la capa siguiente, por lo que se dice que es una red totalmente conectada.

Figura 3.8: Perceptrón Multicapa en representación matricial.

## 3.4.2. Propagación hacia adelante

El Perceptrón multicapa define una relación entre las variables de entrada y las variables de salida. Dicha relación se establece mediante el cálculo que realiza cada neurona de las entradas que recibe y produce una salida que propaga mediante las conexiones respectivas a la siguiente capa.

El procesamiento realizado para esta arquitectura de red neuronal es el siguiente:

- 1. Activación de las entradas: se transmiten las señales recibidas del exterior hacia dentro de la red.

- 2. Activación de las neuronas de la capa oculta: las neuronas ocultas reciben las señales de entrada y los umbrales, son sumados y al resultado se le aplica la función de activación (tangente sigmoidal o sigmoide).

- 3. Activación de la capa de salida: se realiza un procesamiento similar al de las capas ocultas. En esta capa es común que la función de activación sea la función lineal.

# 3.5. Aprendizaje de la Red Neuronal Artificial

## 3.5.1. Criterios de Finalización

En muchos de los problemas que se resuelven mediante el uso del método Backpropagation, no se puede garantizar que el error de aprendizaje  $(E_{It})$  converja a cero. Sin embargo existen criterios que pueden ser usados para

finalizar el ajuste de los parámetros de acuerdo al problema a resolver. A continuación se presentan los criterios de finalización más utilizados en la implementación de redes neuronales artificiales:

1. Existen algunos problemas cuya complejidad es poca, con lo que el error de la iteración llega a ser cero, es decir, se resuelve en su totalidad el problema, así que también este constituye un criterio de finalización.

$$E_{It} = 0$$

2. Un criterio muy utilizado para detener el entrenamiento de redes neuronales se refiere al hecho de fijar un valor  $(\varepsilon)$  lo suficientemente pequeño como para considerar que la red ha sido entrenada en el caso que el error de iteración caiga por debajo de este valor. Generalmente se tienen valores entre 0,1 y 0,01. Desafortunadamente este criterio puede terminar prematuramente el entrenamiento.

$$E_{It} < \varepsilon$$

3. El criterio más extremo utilizado en el entrenamiento de las redes neuronales consiste en terminar el entrenamiento de la red en el momento que se alcance una cantidad de iteraciones considerable  $(It_{max})$ , esto minimiza el riesgo de que el entrenamiento caiga en un mínimo local.

$$It = It_{max}$$

4. Adicional a estos criterios, se utiliza el algoritmo  $Early\ stopping$  que previene el sobreentrenamiento de la red neuronal. Consiste en que cada n intervalo de iteraciones, se ejecuta una iteración de prueba y se calcula el error, que entonces se nombra como  $error\ de\ validación\ (e_{val})$ ; entonces se reanuda el entrenamiento durante las mismas n iteraciones, al final de las cuales se calcula nuevamente el error, se comparan ambos errores y entonces cuando el error crece dos o más veces consecutivas, se termina el entrenamiento. Los valores de los parámetros finales de la red serán los que se tenían en el instante previo a que el error comenzara a crecer.

# 3.5.2. Diseño de las Reglas de Aprendizaje

El aprendizaje de la Red Neuronal Artificial que se desarrolló en este trabajo está basado en el método del gradiente descendiente, en el que el error se minimiza sucesivamente para cada patrón de entrada. Para ello, es necesario establecer reglas de aprendizaje mediante las siguientes ecuaciones.

$$w(k+1) = w(k) - \alpha \frac{\partial e(k)}{\partial w}$$

(3.6)

$$b(k+1) = b(k) - \alpha \frac{\partial e(k)}{\partial b}$$

(3.7)

donde  $\alpha$  representa la velocidad de convergencia al valor deseado (raz'on de aprendizaje): un valor muy grande ocasiona que la red tarde menos en llegar al objetivo, mientras que uno más pequeño brinda un ajuste más fino [38].

Los valores de w(k) y b(k) cambian mediante las derivadas parciales de e(k) respecto a las variables w y b. A este proceso se les conoce como propagación hacia atrás del error (backpropagation).

Figura 3.9: Red neuronal [2-2-1].

Para desarrollar de mejor manera el algoritmo *Backpropagation* se tomará como ejemplo una red neuronal [2-2-1] como la de la figura 3.9, sus ecuaciones de la propagación hacia adelante son las siguientes:

$$a_1^1 = f^1(w_{11}^1 \cdot p_1 + w_{21}^1 \cdot p_2 + b_1^1)$$

$$a_2^1 = f^1(w_{12}^2 \cdot p_1 + w_{22}^1 \cdot p_2 + b_2^1)$$

$$a^{2} = f^{2}(w_{11}^{2} \cdot a_{1}^{1} + w_{21}^{2} \cdot a_{2}^{1} + b_{1}^{2})$$

$$(3.8)$$

Es necesario tener en cuenta la ecuación del error que será empleada para obtener las reglas de aprendizaje, en este caso se trata del *Error cuadrático* medio descrito por la ecuación (3.9).

$$e(k) = \frac{1}{2}(a_{target} - a^2)^2 \tag{3.9}$$

# Regla de la Cadena

El error en el Perceptrón multicapa no es función explícita de los pesos sinápticos en las capas ocultas, por lo tanto sus derivadas requieren cálculos no triviales. Esto implica utilizar la regla de la cadena para derivar los pesos sinápticos.

Se tiene una función f que es una función explícita de una variable n y se desea derivar f con respecto a una tercer variable w, entonces la regla de la cadena queda como sigue:

$$\frac{df(n(w))}{dw} = \frac{df(n)}{dn} \cdot \frac{dn(w)}{dw}$$

Esto es de utilidad para hallar las derivadas en 3.6 y 3.7.

# Regla $\delta$ generalizada

Con base en las ecuaciones (3.8) y (3.9) se determinan las reglas de aprendizaje de los pesos sinápticos y el umbral de la capa de salida:

$$w_{11}^2(k+1) = w_{11}^2(k) - \alpha \frac{\partial e(k)}{\partial w_{11}^2}$$

$$w_{21}^2(k+1) = w_{21}^2(k) - \alpha \frac{\partial e(k)}{\partial w_{21}^2}$$

$$b_1^2(k+1) = b_1^2(k) - \alpha \frac{\partial e(k)}{\partial b_1^2}$$

Ahora se determinan las reglas de aprendizaje para la capa oculta:

$$\begin{split} w_{11}^1(k+1) &= w_{11}^1(k) - \alpha \frac{\partial e(k)}{\partial w_{11}^1} \\ w_{12}^1(k+1) &= w_{12}^1(k) - \alpha \frac{\partial e(k)}{\partial w_{12}^1} \\ w_{21}^1(k+1) &= w_{21}^1(k) - \alpha \frac{\partial e(k)}{\partial w_{21}^1} \\ w_{22}^1(k+1) &= w_{22}^1(k) - \alpha \frac{\partial e(k)}{\partial w_{22}^1} \\ b_1^1(k+1) &= b_1^1(k) - \alpha \frac{\partial e(k)}{\partial b_1^1} \\ b_2^1(k+1) &= b_2^1(k) - \alpha \frac{\partial e(k)}{\partial b_2^1} \end{split}$$

En las expresiones anteriores aparecen términos que incluyen derivadas parciales, se trata de la regla  $\delta$  generalizada, que serán resueltos mediante la regla de la cadena antes expuesta. La regla  $\delta$  generalizada tendrá las siguientes formas:

- ▶ Capa de salida

- Pesos sinápticos

$$\frac{\partial e(k)}{\partial w_{i1}^2} = \frac{\partial e(k)}{\partial a} \cdot \frac{\partial a}{\partial f^2} \cdot \frac{\partial f^2}{\partial w_{i1}^2}

= -(a_{target} - a^2) \cdot 1 \cdot a_i^1

= -(a_{target} - a^2) \cdot a_i^1$$

(3.10)

• Bias

$$\frac{\partial e(k)}{\partial b_1^2} = \frac{\partial e(k)}{\partial a} \cdot \frac{\partial a}{\partial f^2} \cdot \frac{\partial f^2}{\partial b_1^2}

= -(a_{target} - a^2) \cdot 1 \cdot 1

= -(a_{target} - a^2)$$

(3.11)

▶ Capa oculta

Pesos sinápticos

$$\frac{\partial e(k)}{\partial w_{ij}^{1}} = \frac{\partial e(k)}{\partial a^{2}} \cdot \frac{\partial a^{2}}{\partial f^{2}} \cdot \frac{\partial f^{2}}{\partial a_{j}^{1}} \cdot \frac{\partial a_{j}^{1}}{\partial f^{1}} \cdot \frac{\partial f^{1}}{\partial w_{ij}^{1}}$$

$$= -(a_{target} - a^{2}) \cdot 1 \cdot w_{ij}^{1} \cdot f^{1}(1 - f^{1}) \cdot p_{i}$$

$$= -(a_{target} - a^{2}) \cdot w_{ij}^{1} \cdot f^{1}(1 - f^{1}) \cdot p_{i}$$

(3.12)

• Bias

$$\frac{\partial e(k)}{\partial b_j^1} = \frac{\partial e(k)}{\partial a^2} \cdot \frac{\partial a^2}{\partial f^2} \cdot \frac{\partial f^2}{\partial a_j^1} \cdot \frac{\partial a_j^1}{\partial f^1} \cdot \frac{\partial f^1}{\partial b_j^1}$$

$$= -(a_{target} - a^2) \cdot 1 \cdot w_{ij}^1 \cdot f^1(1 - f^1)$$

$$= -(a_{target} - a^2) \cdot w_{ij}^1 \cdot f^1(1 - f^1) \tag{3.13}$$

En las ecuaciones anteriores hay dos índices: i y j, éstos se refieren al número de la neurona origen y a la neurona destino respectivamente. Una vez que se tienen desarrollados los términos mediante la regla de la cadena, las reglas de aprendizaje quedan como sigue:

Capa de salida

$$w_{11}^{2}(k+1) = w_{11}^{2}(k) - \alpha(-(a_{target} - a^{2}) \cdot a_{1}^{1})$$

$$w_{21}^{2}(k+1) = w_{21}^{2}(k) - \alpha(-(a_{target} - a^{2}) \cdot a_{2}^{1})$$

$$b_{1}^{2}(k+1) = b_{1}^{2}(k) - \alpha(-(a_{target} - a^{2}))$$

Capa oculta

$$w_{12}^{1}(k+1) = w_{12}^{1}(k) - \alpha \cdot (-(a_{target} - a^{2}) \cdot w_{11}^{2} \cdot f_{1}(1 - f_{1}) \cdot p_{1}$$

$$w_{11}^{1}(k+1) = w_{11}^{1}(k) - \alpha \cdot (-(a_{target} - a^{2}) \cdot w_{11}^{2} \cdot f_{1}(1 - f_{1}) \cdot p_{1}$$

$$b_1^1(k+1) = b_1^1(k) - \alpha \cdot (-(a_{target} - a^2) \cdot w_{11}^2 \cdot f_1(1 - f_1))$$

$$w_{21}^1(k+1) = w_{21}^1(k) - \alpha \cdot (-(a_{target} - a^2) \cdot w_{21}^2 \cdot f_1(1 - f_1) \cdot p_2$$

$$w_{22}^1(k+1) = w_{22}^1(k) - \alpha \cdot (-(a_{target} - a^2) \cdot w_{21}^2 \cdot f_1(1 - f_1) \cdot p_2$$

$$b_2^1(k+1) = b_2^1(k) - \alpha \cdot (-(a_{target} - a^2) \cdot w_{11}^2 \cdot f_1(1 - f_1)$$

#### Cálculo de Sensitividades

De las ecuaciones 3.10, 3.11, 3.12 y 3.13 es posible factorizar algunos términos comunes y así, facilitar el procedimiento de cálculo. El primer término a factorizar es la Sensitividad de la capa de salida  $(S^2)$ .

$$S^2 = -(a_{target} - a^2) (3.14)$$

Entonces se redefinen las reglas de aprendizaje de la capa de entrada, a las ecuaciones 3.12 y 3.13 se factorizan nuevamente los términos en común. El nuevo término será la Sensitividad de la capa oculta  $(S_i^1)$ .

$$\frac{\partial e(k)}{\partial w_{ij}^{1}} = \frac{\partial e(k)}{\partial a} \cdot \frac{\partial a}{\partial f^{2}} \cdot \frac{\partial f^{2}}{\partial a_{j}^{1}} \cdot \frac{\partial a_{j}^{1}}{\partial f^{1}} \cdot \frac{\partial f^{1}}{\partial w_{ij}^{1}}$$

$$S_{i}^{1} = S^{2} \cdot w_{ij}^{2} \cdot f^{1}(1 - f^{1}) \tag{3.15}$$

El término  $f^1(1-f^1)$  corresponde a la derivada de la función de activación de las neuronas de la capa oculta (ver Apéndice A); dado que la función presente en la neurona de la capa de salida es la función lineal y su primer derivada es 1, no aparece explícita. Como resultado de las factorización de las Sensitividades se tienen las siguientes reglas de aprendizaje:

▶ Capa de salida

$$w_{11}^{2}(k+1) = w_{11}^{2}(k) - \alpha \cdot S^{2} \cdot a_{1}^{1}$$

$$w_{21}^{2}(k+1) = w_{21}^{2}(k) - \alpha \cdot S^{2} \cdot a_{2}^{1}$$

$$b_1^2(k+1) = b_1^2(k) - \alpha \cdot S^2$$

▶ Capa oculta

$$\begin{split} w_{11}^1(k+1) &= w_{11}^1(k) - \alpha \cdot S_1^1 \cdot p_1 \\ w_{12}^1(k+1) &= w_{12}^1(k) - \alpha \cdot S_2^1 \cdot p_1 \\ \\ b_1^1(k+1) &= b_1^1(k) - \alpha \cdot S_1^1 \\ \\ w_{21}^1(k+1) &= w_{21}^1(k) - \alpha \cdot S_1^1 \cdot p_2 \\ \\ w_{22}^1(k+1) &= w_{22}^1(k) - \alpha \cdot S_2^1 \cdot p_2 \\ \\ b_2^1(k+1) &= b_2^1(k) - \alpha \cdot S_2^1 \end{split}$$

# 3.5.3. Ecuaciones Generales

En el momento en el que ya se tienen las reglas de aprendizaje, es posible obtener formas generales para cada uno de los parámetros de la red neuronal [40].

# Propagación hacia adelante

Las ecuaciones generales de la propagación hacia adelante de las señales de entrada para una red neuronal de M capas son las siguientes:

$$a^{0} = P$$

$$a^{m+1} = F^{m+1}(W^{m+1} \cdot a^{m} + b^{m+1})$$

$$a = a^{M}$$

(3.16)

donde m = 0, 1, 2, M - 1.

# Aprendizaje

Como parte de la retropropagación, es necesario conocer las Sensitividades tanto de las capas ocultas como de la capa de salida, las cuales están definidas por:

$$S^M = -\dot{F}^M(n^M) \cdot (a_{target} - a^2) \tag{3.17}$$

$$S^{m} = \dot{F}^{m}(n^{m}) \cdot (W^{m+1})^{T}(S^{m+1})$$

(3.18)

para  $M=M-1,\cdots,2,1$  y donde  $\dot{F^m}$  es la derivada de la función de activación de las capas ocultas, mientras que  $\dot{F^M}$  es la derivada de la función de la capa de salida. Las Reglas de aprendizaje de los pesos sinápticos y los bias de la red neuronal artificial quedan de la siguiente manera:

$$W^{m}(k+1) = W^{m}(k) - \alpha S^{m}(a^{m-1})^{T}$$

(3.19)

$$b^{m}(k+1) = b^{m}(k) - \alpha S^{m} \tag{3.20}$$

# 3.5.4. Proceso de aprendizaje

Se tiene un conjunto  $\{(p_1(1), a_{target1}(1)), \dots, (p_n(k), a_{targetn}(k))\}$  de patrones de entrada para el problema, entonces el proceso de aprendizaje se describe a continuación:

Paso (1). Se toma un conjunto de muestras y se divide de la siguiente manera:

- ▷ 70 % datos de entrenamiento

- ▶ 15 % datos de validación

- ⊳ 15 % de prueba

Paso (2). Se inicializan de forma aleatoria los pesos sinápticos y los umbrales dentro del rango [-1,1].

- Paso (3). Se aplica como entrada a la red un patrón del conjunto de entrenamiento obteniendo una salida a.

- Paso (4). Se calcula el error mediante la ecuación (3.9).

- Paso (5). Utilizando el error obtenido en el paso anterior, se aplican las reglas de aprendizaje para cada uno de los parámetros de la red mediante las ecuaciones (3.19) y (3.20).

- Paso (6). Se repiten desde Paso (3) hasta Paso (5) para todos los valores del conjunto de entrenamiento.

- Paso (7). Se calcula el error de iteración  $(E_{it})$ , que en este punto toma en nombre de *Error de entrenamiento*.

- Paso (8). Se repite Paso (3) a Paso (7) hasta cumplir alguno de los cuatro criterios de finalización:

- $a) E_{it} = 0$

- b)  $E_{it} \leq \varepsilon$

- c) Alcanzar un  $It_{max}$

- d) Early Stopping

En el segundo y tercer criterio de finalización se utilizan dos parámetros importantes que se definen a continuación:

- $\triangleright$   $\varepsilon$ : valor mínimo que se establece para continuar con el proceso de entrenamiento de la red neuronal.

- $\triangleright It_{max}$ : número máximo de iteraciones que serán ejecutadas en el entrenamiento de la red neuronal.

Estos criterios previenen que la red neuronal caiga en mínimos locales, o bien, que la red sea sobreentrenada y que sus resultados para la propagación hacia adelante de las entradas presente grandes fallas [41].

# 3.6. Resumen

A lo largo de este capítulo se describieron todos aquellos aspectos teóricos que rigen el comportamiento de las redes neuronales artificiales, en especial el modelo *Perceptrón multicapa*. Al describir este modelo, se incluyen las ecuaciones útiles para realizar la propagación hacia adelante (*Feed-Forward*) del mismo. Esto se debe al uso de las redes neuronales como metodología para diseñar el sensor virtual propuesto.

El algoritmo de aprendizaje conocido como *Backpropagation* también fue descrito, con la finalidad de brindarle al lector el fundamento matemático que se tomó como base para el desarrollo de la implementación en un FPGA del algoritmo de aprendizaje.

# Desarrollo de la Investigación

La implementación del sensor virtual basado en el algoritmo de aprendizaje *Backpropagation* para una Red Neuronal Artificial se realizó en una tarjeta Altera DE2-70 (figura 4.1) que incluye un FPGA de la serie Cyclone II, el cual contiene cerca de 70,000 LEs y poco más de 1 MB de memoria RAM [42].

Figura 4.1: Tarjeta Altera DE2 70.

# 4.1. Panorama General

Esta implementación consta de dos etapas principalmente: la propagación hacia adelante de las señales de entrada (feedforward) y la propagación hacia atrás del error que se presenta a cada ejecución de un patrón de entrada a la red neuronal (backpropagation).

La estructura del proyecto se basa en la construcción. Algunos de estos módulos fueron programados, los demás corresponden a plantillas que provee Altera mediante el entorno de desarrollo Quartus II.

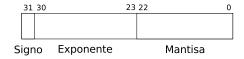

Las platillas corresponden a memorias ROM y RAM, unidades de artimética de punto flotante (sumadores, restadores, multiplicadores, divisores) y a convertidores de *Integer* a punto flotante y viceversa. Todos los datos con los que realiza cálculos la red neuronal tienen un formato de punto flotante de 32 bits, cuya estructura se muestra en la figura 4.2.

Figura 4.2: Formato de punto flotante de 32 bits.

El bit más significativo corresponde al signo (1: negativo, 0: positivo), los siguientes 8 bits (30-23) corresponden al exponente y los restantes 23 bits (22-0) serán utilizados para la mantisa, que define la parte fraccionaria del número.

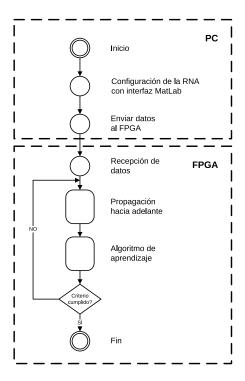

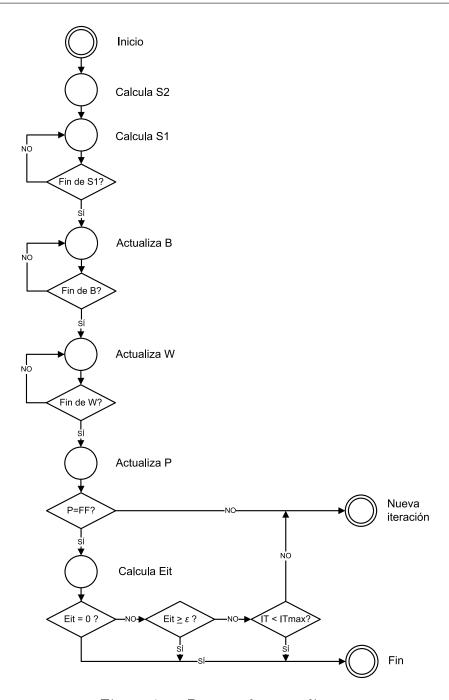

En la figura 4.3 se muestra el proyecto de una forma general, en la que se observa el procesamiento que lleva a cabo el FPGA para realizar el entrenamiento:

#### ⊳ PC

- 1. Configuración de la RNA con interfaz MatLab: la aplicación desarrollada en MatLab permite al usuario el modelado de la red neuronal, elige la estructura, e ingresa el conjunto de entrenamiento y los parámetros para fijar parámetros del entrenamiento ( $\varepsilon$  y  $\gamma$ ).

- 2. Envío de datos al FPGA: convierte los datos (pesos sinápticos, bias, parámetros de configuración) que se encuentran en un formato comprensible por la PC a un formato de punto flotante IEEE que es utilizado por los módulos del FPGA y los envía vía puerto serial al FPGA.

Figura 4.3: Diagrama general de la Red Neuronal y su aprendizaje.

#### ⊳ FPGA

- 1. Recepción de datos: el FPGA recibe los datos y los almacena en sus memorias respectivas para su posterior uso en los cálculos.

- 2. Propagación hacia adelante: calcula la salida de la red con los pesos sinápticos, bias y entradas que en ese momento tenga la red.

- 3. Algoritmo de aprendizaje: modifica los pesos sinápticos y bias conforme al error obtenido en cada iteración, también actualiza el valor de las entradas a los siguientes para que sean ejecutados en una futura propagación hacia adelante.

- 4. Verificación de criterios de finalización: se revisan los criterios de finalización y su relación con los parámetros que han sido dados por el usuario para una posible terminación del entrenamiento de la red neuronal.

# 4.2. Propagación hacia adelante de las señales

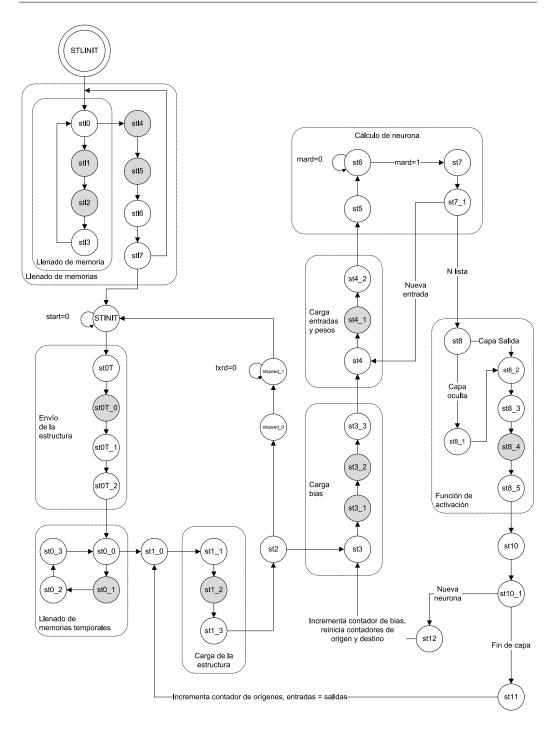

La etapa de propagación hacia adelante consiste en el hecho de aplicar las ecuaciones de propagación hacia adelante de las señales de entrada a la red neuronal, por ello se implementó una máquina de estados finitos (FSM, siglas del inglés *Finite State Machine*). Dicha FSM controla todas las transiciones entre los estados que realizan diversas funciones: carga de datos en memorias, cálculos, entre otros.

La figura 4.4 ilustra la ejecución de la FSM, en la que se observan estados cuyo color más oscuro, esto indica que son estados de retardo para ajustarse a tiempos de almacenamiento o lectura en memoria, o bien, de espera de fin de ejecución de módulos. Por otra parte, se observan también bloques que delimitan las etapas por las que pasa lan los datos para llegar al punto final de la ejecución de la red neuronal en su totalidad. Los bloques que intervienen en el procesamiento son los siguientes:

- ▷ Llenado de memorias: los datos recibidos vía puerto serial se almacenan en las memorias respecivas. La interfaz de MatLab envía los datos en una secuencia que el FPGA mantiene con la finalidad de guardar los datos donde corresponde. La mayoría de las memorias son de tipo RAM, a excepción de dos ROM, que son las tablas LUT para los para la Abscisa y la Pendiente utilizadas para la función sigmoidal.

- Carga de la estructura: los valores de la cadena de la estructura se cargan para ejecutar la red neuronal, existen dos índices: origen es el número de neuronas de la capa actual y destino, el número de neuronas de la capa siguiente.

- Cálculo de neurona: una vez que se tienen listos los valores de las entradas al módulo que realiza las funciones de una neurona, se procede a su

respectivo cómputo. Cuándo existe más de una entrada, se ejecuta la carga de pesos y entradas hasta que se resuelve la sumatoria de todas las entradas y el bias. En apartados posteriores se aborda con mayor profundidad el procesamiento realizado por el módulo *Multadder*.

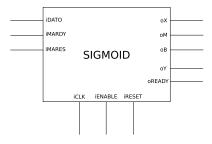

⊳ Función de activación: este bloque calcula la salida de una neurona, ya sea mediante la función lineal o la sigmoidal. Este bloque se revisa con mayor detenimiento en secciones posteriores.

Figura 4.4: Máquina de Estados de la propagación hacia adelante de la Red Neuronal Artificial.

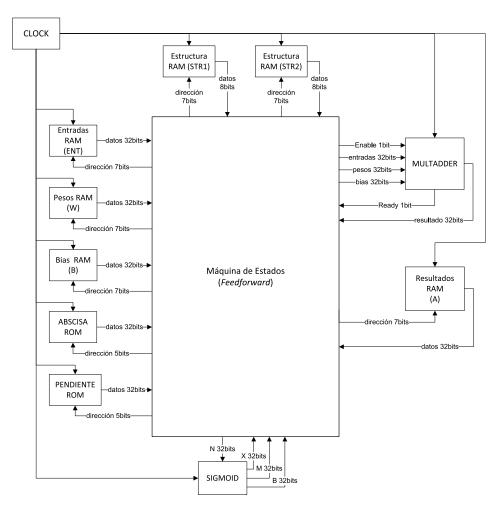

La figura 4.5 muestra los puertos con los que se comunican los módulos con la FSM principal, en la parte superior están las dos memorias RAM en las que se almacena la estructura para controlar el flujo de las operaciones entre las capas de la red neuronal. En el lado izquierdo de la figura, se encuentran las memorias de datos que son utilizadas para los cálculos: pesos sinápticos, bias, entradas, abscisa y pendiente; en la parte derecha aparece el módulo *Multadder* y la memoria de los resultados de las neuronas de la red; mientras que en la parte inferior se observa el módulo *Sigmoid*, que se encarga de obtener el valor de la función de activación de las neuronas de la red neuronal.

Figura 4.5: Arquitectura general de la propagación hacia adelante.

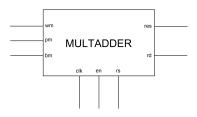

#### 4.2.1. Módulo Multadder

Durante el cálculo de la propagación hacia adelante de las señales de entrada a la red neuronal destaca por su importancia el módulo *Multadder* (figura 4.6), que es fundamentalmente una neurona artificial en hardware con una sola entrada. Este módulo funciona de la misma manera en que la figura 3.5, acumula los productos de entradas-pesos sinápticos y bias.

Figura 4.6: Módulo Multadder.

Una neurona de una sola entrada se puede convertir a una neurona multientrada conforme el Algoritmo 4.1.

#### Algoritmo 4.1 Conversión de una neurona simple a multientrada

Entrada: R: número de entradas,

w[i]: pesos sinápticos de la neurona,

p[i]: entradas a la neurona,

b : bias de la neurona

Salida: A : salida de la neurona

1:  $s_0 \leftarrow b$

2: mientras  $i \leq R$  hacer

$3: \quad s_i \leftarrow w_i * p_i + s_{i-1}$

4: fin mientras

5:  $n \leftarrow s_n$

6:  $A \leftarrow f(n)$

El módulo Multadder devuelve el valor n en el que se encuentran acumulados todos los productos de las entradas y el bias de la neurona.