INSTITUTO POLITÉCNICO NACIONAL CENTRO DE INVESTIGACIÓN EN COMPUTACIÓN

**Artificial Intelligence and Embedded Systems Laboratories**

### Generating Optimal Functional Coverages in Digital Systems

# THESIS

A doctoral dissertation submitted by M. Sc. Alfonso Martínez Cruz

> For the degree of Doctor of Computer Science

> > Advisors

Ricardo Barrón Fernández, Ph.D. Herón Molina Lozano, Ph.D.

Mexico city,

January 2016

SIP-14 BIS

### INSTITUTO POLITÉCNICO NACIONAL SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

#### ACTA DE REVISIÓN DE TESIS

En la Ciudad de México, D.F. siendo las 14:00 horas del día 4 del mes de diciembre de 2015 se reunieron los miembros de la Comisión Revisora de la Tesis, designada por el Colegio de Profesores de Estudios de Posgrado e Investigación del:

Centro de Investigación en Computación

para examinar la tesis titulada:

"Generating Optimal Functional Coverages in Digital Systems"

| sentada por el alumno:<br>MARTÍNEZ | CRUZ             |   |   | ALFO | NSO     |   |   |  |

|------------------------------------|------------------|---|---|------|---------|---|---|--|

| Apellido paterno                   | Apellido materno |   |   | . N  | ombre(s | ) |   |  |

|                                    | Con registro:    | A | 1 | 2    | 0       | 9 | 0 |  |

aspirante de: DOCTORADO EN CIENCIAS DE LA COMPUTACIÓN

Después de intercambiar opiniones los miembros de la Comisión manifestaron APROBAR LA TESIS, en virtud de que satisface los requisitos señalados por las disposiciones reglamentarias vigentes.

#### LA COMISIÓN REVISORA

Directores de tesis

Dr. Ricardo Barrón Fernández

Dr. Sergio Suárez Guerra

Dr. Salvador Godoy Calderón

é

Dr. Herón Molina Lozano

Dr. Victor Hugo Ponce Ponce

的用意识的最高效以

DIRECCION

Vargas

Dr Marco Antonio Ramirez Salinas

PRESIDENTE DEL COLEGIO DE PROFESORES

onso Villa

3

### INSTITUTO POLITÉCNICO NACIONAL SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

#### CARTA CESIÓN DE DERECHOS

En la Ciudad de <u>México</u>, el día <u>7</u> del mes <u>Enero</u> del año <u>2016</u>, el que suscribe <u>Alfonso Martínez Cruz</u> alumno del Programa de <u>Doctorado en Ciencias de la computación</u> con número de registro <u>A120902</u>, adscrito al <u>Centro de Investigación en Computación</u>, manifiesta que es autor (a) intelectual del presente trabajo de Tesis bajo la dirección de <u>Dr. Ricardo Barrón Fernández y Dr. Herón Molina Lozano</u>, y cede los derechos del trabajo intitulado <u>Generating Optimal Functional Coverages in Digital Systems</u>, al Instituto Politécnico Nacional para su difusión, con fines académicos y de investigación.

Los usuarios de la información no deben reproducir el contenido textual, gráficas o datos del trabajo sin el permiso expreso del autor y/o director del trabajo. Este puede ser obtenido escribiendo a la siguiente dirección <u>mcruzb09@sagitario.cic.ipn.mx</u>. Si el permiso se otorga, el usuario deberá dar el agradecimiento correspondiente y citar la fuente del mismo.

Mulo

Alfonso Martinez Cruz

## Resumen

El constante avance de la tecnología y los nuevos requerimientos en el desempeño y producción de los sistemas digitales han requerido que nuevos esquemas de verificación y prueba sean propuestos. Como hace unas décadas Gordon E. Moore predijo que el número de componentes transistores en un circuito integrado se duplicaría cada dos años así como la tendencia del desarrollo de nuevos dispositivos cada ves mas pequeños y con mayor complejidad en su funcionamiento han producido que hoy en día, tengamos a nuestro alcance dispositivos como: smart-phones, smart-watches, tabletas, drones, computadoras, etc. que contienen chips con millones de dispositivos semiconductores procesando gran cantidad de información y realizando diferentes funciones en pequeños intervalos de tiempo.

La verificación funcional representa una parte importante en el proceso de diseño de los sistemas digitales debido a que los errores en hardware resultan más costosos y es necesario remplazar los dispositivos físicamente. En el presente trabajo de investigación se propone un nuevo método de generación de altos porcentajes de coberturas funcionales para la verificación de sistemas digitales. El método propuesto esta basado en la aplicación de meta-heurísticas (Particle Swarm Optimización, Differential evolution algorithm), el uso de modelos de cobertura funcional y la simulación de los dispositivos bajo verificación. Dicho método representa un método hibrido y a la ves una alternativa para complementar las técnicas actuales utilizadas para realizar la verificación funcional.

A diferencia de los trabajos previos donde se han utilizado algoritmos genéticos, en esta investigación otras meta-heurísticas como: Particle Swarm Optimización algorithm, Differential Evolution algorithm son utilizadas para la generación de vectores de prueba que maximicen los valores de cobertura funcional. Estas meta-heurísticas han sido utilizadas en diferentes problemas de optimización obteniendo resultados competitivos. También, en esta investigación se propone una nueva versión del algoritmo de evolución diferencial compacto para la representación binaria. Dicho algoritmo esta basado en el principio del algoritmo genético compacto ya que utiliza los valores estadísticos para representar a la población, por lo tanto, requiere menos recursos de memoria para su implementación que los algoritmos basados en la población.

Para realizar la prueba de la implementación a nivel RTL han sido diseñadas diferentes herramientas de software. Debido a esto, una plataforma de software ha sido diseñada para

conectar las herramientas de simulación con los módulos en lenguaje de alto nivel. Esta plataforma esta basada en los esquemas actuales para llevar a cabo la verificación por medio de de la simulación de los dispositivos. La plataforma contiene un conjunto de módulos que permiten utilizar diferentes algoritmos, escenarios de prueba, así como conectar las implementaciones de los dispositivos con el entorno de pruebas.

## Abstract

The constant advance of technology and new requirements in the performance and production of new digital systems have required new testing, and verification schemes. A few decades ago Gordon E. Moore predicted that the number of transistors on the components of an integrated circuit would double every two years. Moreover, the new development trends in devices allow for even smaller circuits, that perform more complex operations, permitting the existence of devices such as smart-phones, smart-watches, tablets, drones, computers, etc. containing chips with millions of semiconductors, with a wealth of information processing and performing many different functions in short time periods.

Functional verification represents an important design process partly because the errors in hardware are very expensive and necessitate the replacement of the device. In this research a new test generation method is proposed in order to obtain high rates of coverage for functional verification of digital systems. The proposed method is based on the application of metaheuristic algorithms (Particle Swarm Optimization, Differential evolution algorithm), using functional coverage models and simulation devices under verification. This is a hybrid method and represents an alternative complementing existing techniques used for functional verification.

Unlike previous studies where genetic algorithms have been used, this research provides other meta-heuristics such as a Particle Swarm Optimization algorithm, and a differential evolution algorithm which are used to generate test vectors that maximize the functional coverage values. These meta-heuristics have been used in different optimization problems obtaining competitive results. Moreover, this research proposes a new version of the compact differential evolution algorithm for binary representation. This algorithm is based on the principle of a compact genetic algorithm that uses statistical information in order to represent the population; therefore, it requires less memory resources for implementation than algorithms based on population.

In order to perform the device implementation test in a Register Transfer Level (RTL) different software tools have been designed. Due to this, a software platform is proposed to connect the simulation tools with the modules in high level language. This platform is based on current schemes to conduct verification through simulation devices. The platform contains a set of modules that may use different algorithms, and test scenarios, as well as implementations connecting devices to the test environment.

# Agradecimientos

**GRACIAS** A mis padres Josefina y Gabriel y a mi familia por darme la oportunidad de crecer, desarrollarme y cumplir mis metas.

**GRACIAS** A mis directores de tesis: Dr. Ricardo y Dr. Heron por guiarme y compartir sus experiencias durante mis estudios de doctorado.

**GRACIAS** Al profesor Kwang-Ting (Tim) Cheng por todo su apoyo y sus enseñanzas durante mi estancia en la Universidad de California en Santa Barbara (UCSB).

**GRACIAS** Al Instituto Politécnico Nacional por permitirme realizar mi formación durante mis estudios de doctorado.

**GRACIAS** A mis profesores durante mi estancia en el Centro de Investigación en Computación por compartir su conocimiento y formar parte de mi preparación en mis estudios de doctorado.

**GRACIAS** Al Consejo Nacional de Ciencia y Tecnología, CONACyT, por el apoyo económico proporcionado durante la realización de mis estudios de doctorado. Agradezco a la Secretaria de Investigación y Posgrado del Instituto Politécnico Nacional a través de los proyectos SIP-20151625 y SIP-20151454.

**GRACIAS** A mis compañeros y amigos por compartir sus consejos, experiencias y por su apoyo durante mis estudios. A Lawrence y Bonnie Blakley por su apoyo y atencion durante este trabajo.

"Humility, preparation and your actions make you a better person." Alfonso Martínez Cruz "Sometimes when we want to be better, we need to keep in a box the goals we have already achieved. That box is always carried with us, because we will have difficulties on the road and at that time, the goals in that box will be links to achieve a new proposed goal."

alfonso martínez

# Content

| Resumen         | Ι    |

|-----------------|------|

| Abstract        | III  |

| Agradecimientos | V    |

| Figures         | XII  |

| Tables          | XIII |

| Ι | Int   | roduction                                  | 1  |  |  |  |  |  |  |

|---|-------|--------------------------------------------|----|--|--|--|--|--|--|

| 1 | Intro | Introduction                               |    |  |  |  |  |  |  |

|   | 1.1   | Functional Verification of Digital Systems | 5  |  |  |  |  |  |  |

|   |       | 1.1.1 Elements of Functional Verification  | 8  |  |  |  |  |  |  |

|   | 1.2   | Problem to Solve                           | 9  |  |  |  |  |  |  |

|   | 1.3   | Justification                              | 11 |  |  |  |  |  |  |

|   | 1.4   | General Objective                          | 11 |  |  |  |  |  |  |

|   |       | 1.4.1 Specific Objectives                  | 11 |  |  |  |  |  |  |

|   | 1.5   | Research and developed method              | 11 |  |  |  |  |  |  |

|   | 1.6   | Scope of work                              | 12 |  |  |  |  |  |  |

|   | 1.7   | Contributions                              | 12 |  |  |  |  |  |  |

|   | 1.8   | Organization                               | 13 |  |  |  |  |  |  |

|   | 1.9   | Resume                                     | 13 |  |  |  |  |  |  |

### II State of the Art

| 1 | 5 |

|---|---|

| 1 | Э |

| 2       | State              | e of the                                                                                                       | Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                                                                             |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 2.1                | Introdu                                                                                                        | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                             |

|         | 2.2                | Covera                                                                                                         | ge Directed Test Generation for Functional Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                                                                                                             |

|         | 2.3                | Meta-h                                                                                                         | euristics algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                                                             |

|         | 2.4                | Bayesi                                                                                                         | an Networks and Markov Model approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                                                                                                             |

|         | 2.5                | Metho                                                                                                          | Is based on mutations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24                                                                                                                                             |

|         | 2.6                | Metho                                                                                                          | ls based on data mining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25                                                                                                                                             |

|         | 2.7                | Functio                                                                                                        | onal Test Generation based on extraction of State Machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                                                                             |

|         | 2.8                | Metho                                                                                                          | ls based on Theorem Proving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28                                                                                                                                             |

|         | 2.9                | Metho                                                                                                          | ls based on Model Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                                                                             |

|         | 2.10               | Resum                                                                                                          | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                                                                             |

|         |                    |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                |

|         |                    |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22                                                                                                                                             |

| II      | I D                | igital ]                                                                                                       | Design and Functional Verification of Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33                                                                                                                                             |

| II      | I D                | igital ]                                                                                                       | Design and Functional Verification of Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33                                                                                                                                             |

| II<br>3 |                    | C                                                                                                              | Design and Functional Verification of Digital Systems<br>gn and Functional Verification of Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33<br>35                                                                                                                                       |

|         |                    | tal Desi                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                |

|         | Digit              | tal Desi<br>Digital                                                                                            | gn and Functional Verification of Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35                                                                                                                                             |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital                                                                                            | gn and Functional Verification of Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>35</b><br>36                                                                                                                                |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e                                                                                  | gn and Functional Verification of Digital Systems         systems design         lements of Functional Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>35</b><br>36<br>39                                                                                                                          |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e<br>3.2.1                                                                         | gn and Functional Verification of Digital Systems         systems design         lements of Functional Verification         Functional Coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>35</b><br>36<br>39<br>41                                                                                                                    |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e<br>3.2.1<br>3.2.2                                                                | gn and Functional Verification of Digital Systems         systems design         lements of Functional Verification         Functional Coverage         Coverage Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>35</b><br>36<br>39<br>41<br>43                                                                                                              |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e<br>3.2.1<br>3.2.2<br>3.2.3                                                       | gn and Functional Verification of Digital Systems         systems design         lements of Functional Verification         Functional Coverage         Coverage Points         Functional Coverage Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>35</li> <li>36</li> <li>39</li> <li>41</li> <li>43</li> <li>45</li> </ul>                                                             |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                              | gn and Functional Verification of Digital Systems         systems design         lements of Functional Verification         Functional Coverage         Coverage Points         Functional Coverage Metrics         Calculation of Functional Coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>35</li> <li>36</li> <li>39</li> <li>41</li> <li>43</li> <li>45</li> <li>47</li> </ul>                                                 |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5                                     | gn and Functional Verification of Digital Systems         systems design         lements of Functional Verification         Functional Coverage         Coverage Points         Functional Coverage Metrics         Calculation of Functional Coverage         Functional Coverage Model description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>35</li> <li>36</li> <li>39</li> <li>41</li> <li>43</li> <li>45</li> <li>47</li> <li>49</li> </ul>                                     |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6                            | gn and Functional Verification of Digital Systems         systems design         lements of Functional Verification         Functional Coverage         Coverage Points         Functional Coverage Metrics         Calculation of Functional Coverage         Functional Coverage Metrics         Subscription         Subscription | <ul> <li>35</li> <li>36</li> <li>39</li> <li>41</li> <li>43</li> <li>45</li> <li>47</li> <li>49</li> <li>51</li> </ul>                         |

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7                   | gn and Functional Verification of Digital Systems         systems design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>35</li> <li>36</li> <li>39</li> <li>41</li> <li>43</li> <li>45</li> <li>47</li> <li>49</li> <li>51</li> <li>54</li> </ul>             |

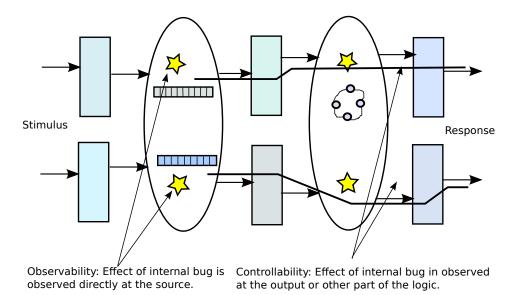

|         | <b>Digi</b><br>3.1 | tal Desi<br>Digital<br>Main e<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9 | gn and Functional Verification of Digital Systems         systems design         systems of Functional Verification         lements of Functional Verification         Functional Coverage         Coverage Points         Functional Coverage Metrics         Calculation of Functional Coverage         Functional Coverage Metrics         Functional Coverage Metrics         Calculation of Functional Coverage         Functional Coverage Model description         Directed Functional Verification for Digital Systems         Controllability and Observability in digital systems         Pseudo-random Constraint Stimulus                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>35</li> <li>36</li> <li>39</li> <li>41</li> <li>43</li> <li>45</li> <li>47</li> <li>49</li> <li>51</li> <li>54</li> <li>55</li> </ul> |

| N | / N  | leta-Heuristics on the Binary Space                                 | 61  |

|---|------|---------------------------------------------------------------------|-----|

| 4 | Met  | a-Heuristics on the Binary Space                                    | 63  |

|   | 4.1  | Binary search space                                                 | 64  |

|   | 4.2  | Evolutionary algorithms                                             | 65  |

|   |      | 4.2.1 Binary Genetic Algorithm                                      | 66  |

|   |      | 4.2.2 Binary Particle Swarm Optimization algorithm (BinPSO)         | 68  |

|   |      | 4.2.3 Binary Differential Evolution Algorithm (DE Algorithm)        | 70  |

|   | 4.3  | Compact meta-heuristic algorithms                                   | 72  |

|   |      | 4.3.1 Compact Binary Genetic algorithm                              | 74  |

|   | 4.4  | Resume                                                              | 76  |

| V | Pr   | oposed Method                                                       | 77  |

| 5 | Proj | oosed Method                                                        | 79  |

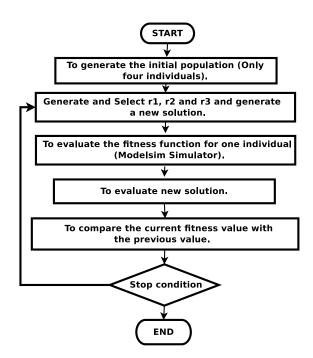

|   | 5.1  | Proposed Compact Binary Differential Evolution Algorithm            | 80  |

|   | 5.2  | Proposed test vector generation method                              | 84  |

|   |      | 5.2.1 Fitness functions                                             | 87  |

|   |      | 5.2.2 Verification platform                                         | 88  |

|   |      | 5.2.3 Applying meta-heuristic algorithms over the proposed platform | 91  |

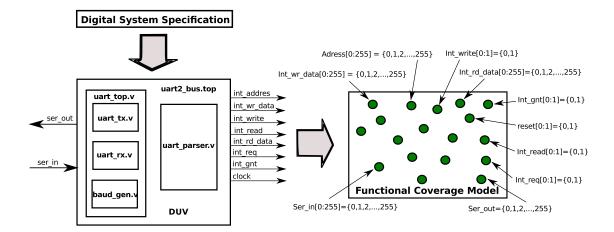

|   |      | 5.2.4 Modeling the Device Under Verification                        | 93  |

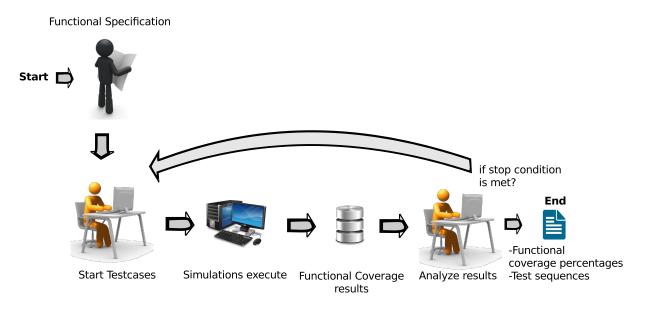

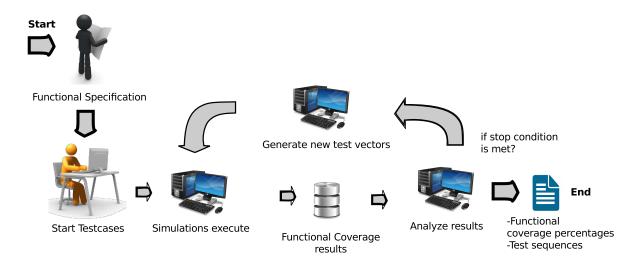

|   |      | 5.2.5 Calculating and analyzing Functional Coverage                 | 95  |

|   |      | 5.2.6 HDL Simulation of the Device Under Verification               | 97  |

|   | 5.3  | Resume                                                              | 98  |

| V | ΙE   | xperiments and Results 1                                            | 101 |

| 6 | Exp  | eriments and Results                                                | 103 |

|   | 6.1  | Case Study                                                          | 104 |

|   |      | 6.1.1 Experimental Setup                                            | 105 |

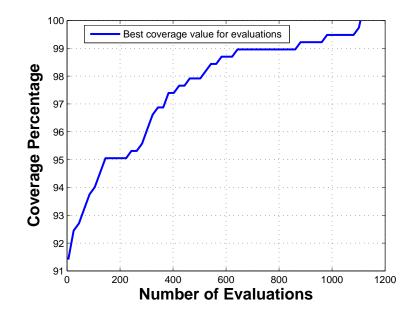

|   |      | 6.1.2 Experiments and Results with Compact-BinDE Algorithm          | 106 |

|   | 6.2  | Experiments and Results with other Meta-heuristic Algorithms        | 115 |

|   |      | 6.2.1 Experiments using a binary Genetic algorithm                  | 116 |

|    |       | 6.2.2   | Experiments using Binary Particle Swarm Optimization algorithm | 119 |

|----|-------|---------|----------------------------------------------------------------|-----|

|    |       | 6.2.3   | Comparison between algorithms                                  | 122 |

|    | 6.3   | Discus  | ssion                                                          | 126 |

|    | Con   | clusio  | ns and future work                                             | 129 |

| 7  | Con   | clusion | s and future work                                              | 131 |

|    |       | 7.0.1   | Conclusions                                                    | 132 |

|    |       | 7.0.2   | Future Work                                                    | 135 |

|    | 7.1   | Contri  | butions                                                        | 136 |

|    |       | 7.1.1   | Published papers in Journals                                   | 136 |

|    |       | 7.1.2   | Published papers in conferences                                | 136 |

| Gl | ossar | У       |                                                                | 139 |

### Bibliography

# Figures

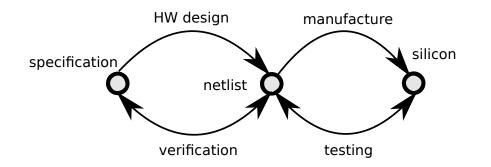

| 1.1  | Testing vs Verification.                                                    | 6   |

|------|-----------------------------------------------------------------------------|-----|

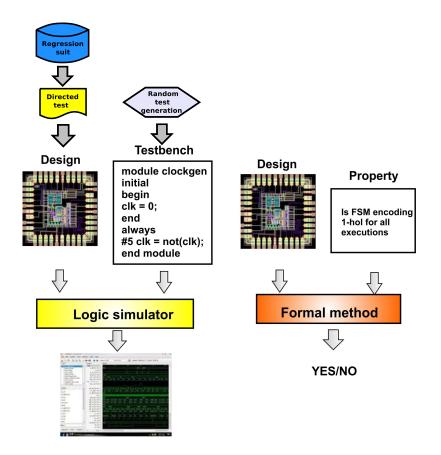

| 1.2  | Functional Verification based on simulation vs Formal Verification          | 7   |

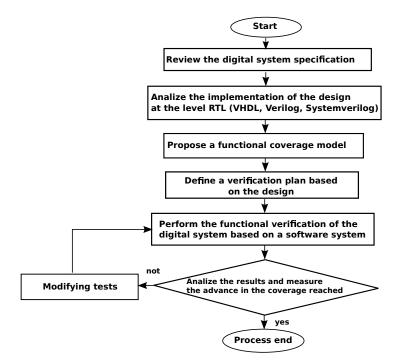

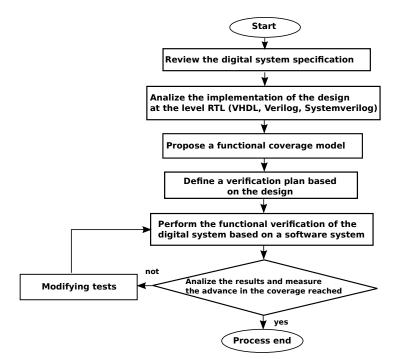

| 1.3  | General methodology for the functional verification process.                | 9   |

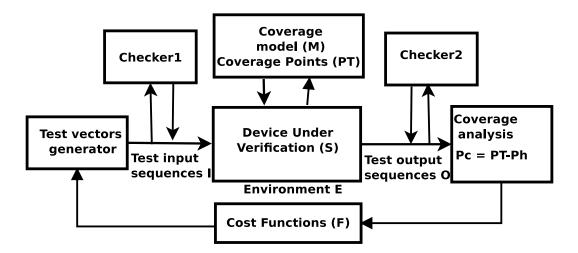

| 2.1  | Coverage Directed Test Generation schema.                                   | 19  |

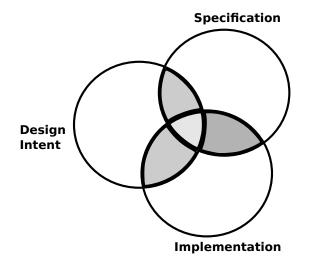

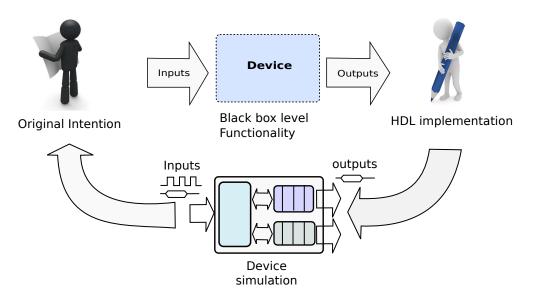

| 3.1  | Design Intention diagram.                                                   | 36  |

| 3.2  | Main steps of digital system design.                                        | 40  |

| 3.3  | General methodology for the functional verification process.                | 41  |

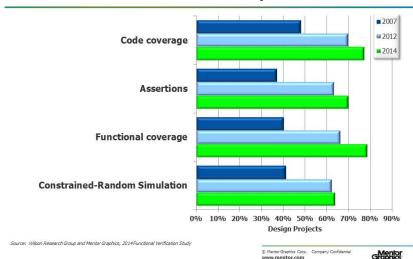

| 3.4  | Trends in Functional Verification Techniques.                               | 43  |

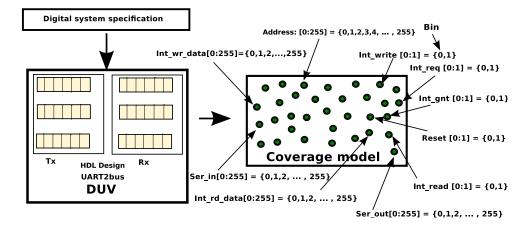

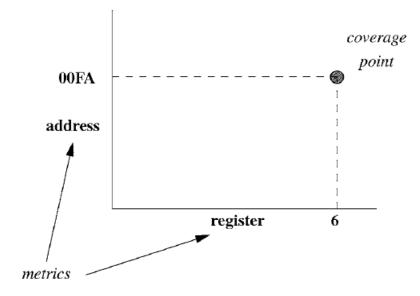

| 3.5  | Model representation of a DUV (UART-bus) using the coverage points          | 50  |

| 3.6  | Coverage Directed Test Generation blocks diagram.                           | 52  |

| 3.7  | Observability and Controllability in a Digital system.                      | 55  |

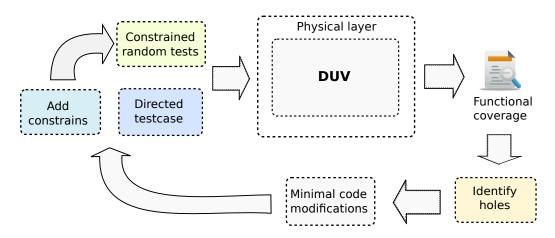

| 3.8  | Constraint random test generation.                                          | 56  |

| 3.9  | Modeling a device through HDL simulation.                                   | 58  |

| 3.10 | Flowchart of verification based on simulation.                              | 59  |

| 3.11 | Trends in Functional Verification Techniques.                               | 60  |

| 4.1  | Generation of new vectors in the Binary Differential Evolution algorithm    | 72  |

| 5.1  | Blocks diagram of the test sequences generation method using CoverPoints    | 86  |

| 5.2  | Verification interface using the proposed Compact-BinDE algorithm.          | 90  |

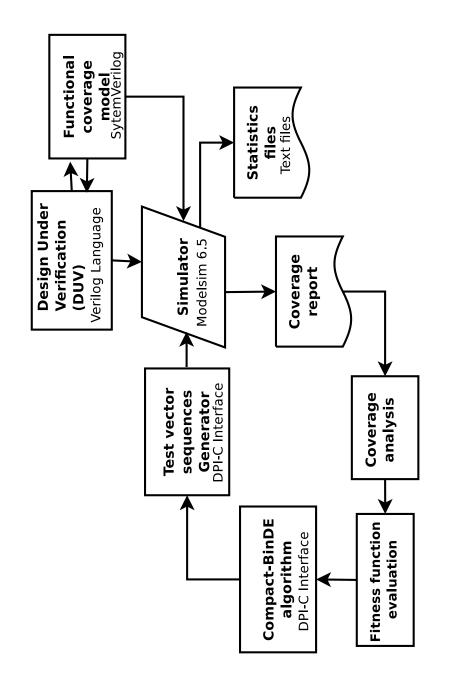

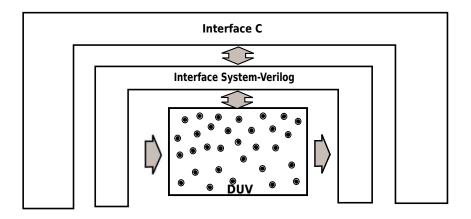

| 5.3  | Schema of the designed platform in order to perform functional verification | 91  |

| 5.4  | Flow Diagram binary GA algorithm using the verification platform.           | 92  |

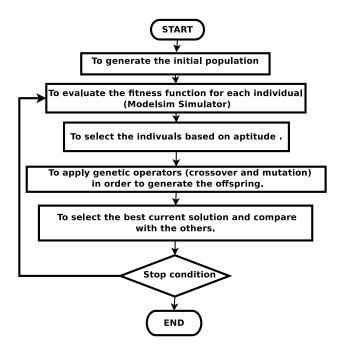

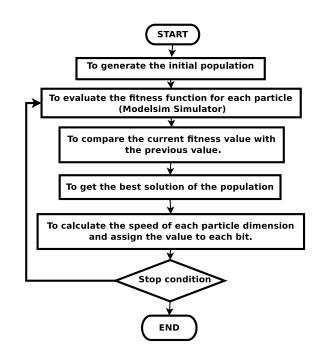

| 5.5  | Flow Diagram PSO algorithm used for generating sequences of vectors         | 93  |

| 5.6  | Flow Diagram Compact-BinDE for generating sequences of vectors.             | 94  |

| 5.7  | Model representation of a DUV (UART-bus) using coverage points              | 95  |

| 5.8  | Manual process to perform the Directed Coverage Functional Verification     | 96  |

| 5.9  | Automated process to perform the Functional Verification.                   | 96  |

| 5.10 | Implemented process to perform the Functional Verification.                 | 99  |

| 5.11 | Modelsim simulator used in the experiments.                                 | 100 |

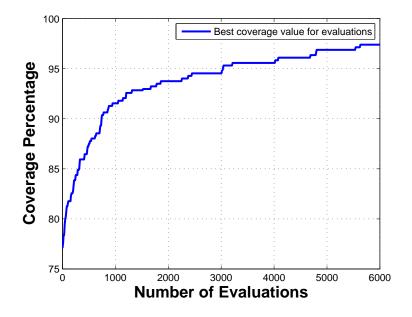

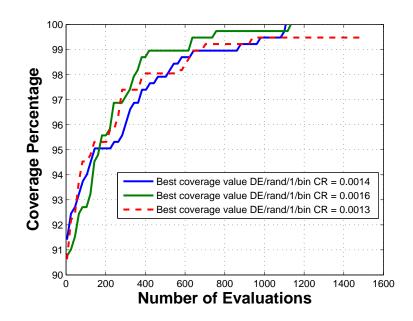

| 6.1 | Coverage values obtained using $f_1$ and the DE/rand/1/bin               | 112 |

|-----|--------------------------------------------------------------------------|-----|

| 6.2 | Comparison of Coverage Directed Test Generation for different scenarios  | 113 |

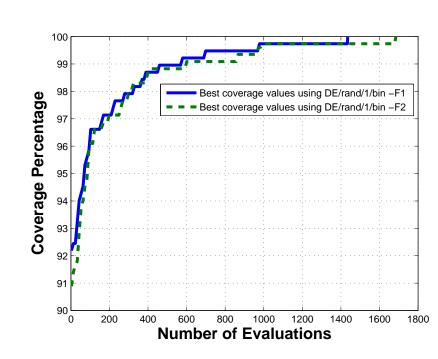

| 6.3 | Coverage Directed Test Generation percentages for different iterations   | 114 |

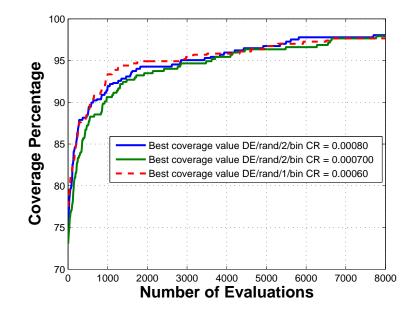

| 6.4 | Comparison of Coverage Directed Test Generation with different CR values | 115 |

| 6.5 | Comparison of Coverage Directed Test Generation using $f1$ and $f2$      | 116 |

| 7.1 | Coverage space example.                                                  | 141 |

## **Tables**

| 2.1  | Works using meta-heuristic algorithms to perform functional verification   | 22  |

|------|----------------------------------------------------------------------------|-----|

| 6.1  | Parameters of four different scenarios using Compact-BinDE algorithm       | 107 |

| 6.2  | Coverage values obtained with four different configurations                | 107 |

| 6.3  | Parameters of four best scenarios using the Compact-BinDE algorithm        | 108 |

| 6.4  | Values of Coverage percentage obtained with different population size      | 108 |

| 6.5  | Parameters of four best scenarios using a solution length of two sequences | 109 |

| 6.6  | Coverage and total time for using different mutation functions             | 109 |

| 6.7  | Parameters of four best scenarios using the UART-IP device                 | 110 |

| 6.8  | Obtained results for four scenarios using Compact-BinDE algorithm          | 110 |

| 6.9  | Compact-BinDE parameters using a length of two sequences for UART-IP       | 111 |

| 6.10 | Results using different configurations of the Compact-BinDE algorithm      | 112 |

| 6.11 | Parameters for experiment using binary Genetic algorithm for FIFO memory . | 117 |

| 6.12 | Results obtained using the binary Genetic algorithm for FIFO memory        | 117 |

| 6.13 | Parameters for experiment using binary Genetic algorithm                   | 118 |

| 6.14 | Results obtained using the binary Genetic algorithm                        | 119 |

| 6.15 | Algorithm parameter values used for PSO scenarios with FIFO memory         | 120 |

| 6.16 | Results obtained for experiment 1 using a FIFO memory                      | 121 |

| 6.17 | Parameters for Particle Swarm Optimization algorithm using a UART device   | 121 |

| 6.18 | Results obtained using the PSO algorithm with a UART bus core              | 122 |

| 6.19 | Results obtained using SR, GA, Compact-BinDE and PSO algorithm             | 123 |

| 6.20 | Parameters for experiment using binary Genetic algorithm                   | 124 |

|      | Results obtained using GA, SR and the Compact-BinDE algorithm              | 124 |

| 6.22 | Results obtained using SR, GA, Compact-BinDE and PSO algorithm             | 126 |

# CHAPTER I

# Introduction

## Chapter 1

## Introduction

Current digital systems have a large amount of resources, performing millions of operations per second. Circuits included in smart-phones, laptops, tablets, etc. permit complex devices to have greater functionality complexity. Due to this, the digital design has a compromise with the market times and technological advances. During the digital systems design process, several steps are involved; one of the most important is design verification. The verification represents the biggest part of the total devices manufacturing cost. The approximate cost of this phase is estimated at about 60% of the total digital system design cost. Unlike software, the errors in hardware designs are very expensive, because these require redesigning and physically replacing the failed device. Also, because of the increase in the functionality complexity and number of transistors of digital systems lately, the importance of creating efficient designs and reducing their verification time has generated the need to create more efficient design verification techniques. It means, techniques that reduce the time and increase the test coverage percentage and because of this, different methods have been developed to perform the verification processes and new software tools have been produced. Furthermore, these software platforms have been used with different digital systems, and the results obtained have shown that it is necessary to develop more efficient methods that can cover all design cases.

The task of checking all input vectors in the device is unfeasible because the coverage space increases as the device complexity also grows. Generally, the main objective of the informal verification techniques is to increase design space coverage and changes for finding errors in the digital systems design. When the verification of an implemented device is performed in a hardware description language (Verilog, SystemC, SystemVerilog, etc), the

verification engineers need to use specialized software tools (Computer Aided Tools-CAD, Questa, Modelsim, Cadence, etc).

Lately, the complexity of digital systems has resulted in the need for new techniques and tools. Different Electronic Design Automation (EDA) Companies provide different software tools in order to perform the steps involved in the functional verification. Different conferences like Digital Automation Conference (DAC), Design Automation and Test in Europe (DATE) have been created in order to publish and share the recent advances concerning digital design, automation techniques among other topics. Researches from industry and academics have published different works related to the verification topic.

Directed Functional Verification has an important role to meet with the conditions during functional verification. It has been detected that the pseudo-random test generation methods are not effective to cover hard cases, therefore, it is necessary to propose new test vector generation methods which can make an efficient search and exercise all functionality.

Three different philosophies have been proposed in order to perform the Functional Verification: Static methods (formal methods), Dynamic methods (Which are based on simulation) and Hybrid methods (which do not fall in formal and informal methods).

Every philosophy contains different strategies in order to test the functionality of a digital system. However, at present, none of these methodologies have been enough to over pass the different problems because the complexity of the functionality of digital systems is increasing. New challenges have appeared, some of them are: compatibility of modules, synchronization of clocks, among others.

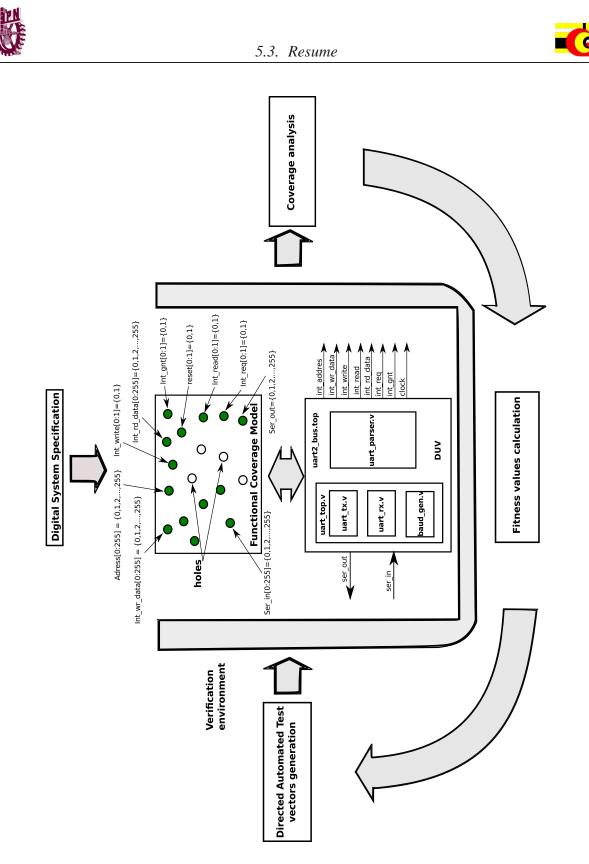

When functional verification is performed, one or more coverage models are used. These coverage models are based on a type of coverage structure or coverage metrics, i.e., finite state machine (FSM), statement, branch path, expression coverage, etc. The coverage model is a fundamental piece for the verification methods representing a golden model to describe the device behavior. Different ways to close the loop between the end of simulation and the new test generation have been proposed. Coverage Directed Test Generation (CDG) has been proposed as a possible solution to this problem. Different experiments have shown that directed probes are promising because a small number of them can reach the same coverage goal with respect to the constrained random probes.

In this research we propose a new method which uses reduced binary meta-heuristics in order to generate sets of test vector sequences. We focus on the hybrid methods (based on the simulation and meta-heuristics) since these methods have obtained good results even though

there is an increase in digital systems complexity. The strategy employed is based on the use of coverage models for the devices verification process, which are built with relevant conditions or coverage points representing the Device Under Verification (DUV) full behavior. The main problem consists in covering all hard cases since the relationships between the CoverPoints and the input data at the design are not trivial. Different to previous works that used meta-heuristics, the proposed method can reduce the number of evaluations used to obtain test sequences that exercise the coverage points.

This chapter presents an introduction to the Functional Verification topic, the problem to solve, the objectives, the justification and the contributions of the present work.

#### **1.1 Functional Verification of Digital Systems**

Functional Verification can be described as the application of information theory where a redundancy and error correction code are required in order to keep the integrity of the information through the design cycle.

Different from the traditional applications of information theory where the message is preserved as it is sent through the communication channel, it is intentionally refined and becomes less abstract during every transformation through the design process. The design process can be described as: incremental clarification put into the communication channel in every stage of the design [1].

In most cases the definition of the Testing and Functional Verification is confused. The testing can be defined as a set of tests applied to the Device Under Verification (DUV) in order to determine if the behavior in each test meets the specification. It is a sample process where not all aspects of the device are exercised, which means that a total subset of all possible device characteristics is used.

In other words, testing consists of a set of stimulus applied to the device in order to test a particular test case or analyze the response of the performance based on the expected behavior. Figure 1.1 shows the testing and the verification into the design process of Digital Systems.

Functional Verification is a comparative process. It includes a wide set of techniques in order to find faults in the behavior of a device. Functional Verification shows if the hardware or software meets the original specification requirements. Also, the functional verification does not show the fault itself. It merely shows the presence of an error.

With the implementation of pseudo-random verification around 1980, it was possible to

Figure 1.1. Testing vs Verification.

explore the design limits using an automated test in order to exercise a range of inherent variability in the functionality of a Digital System. The standard verification consists of:

- A standard context to the analysis which is used for the principles of the pseudo-random functional verification.

- Standard inherent variables in the design.

- Standard interpretation of the specification which is used to define the variables and ranges, rules and guidelines.

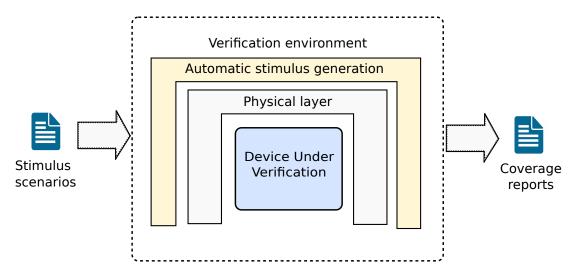

Simulation is most frequently used in Functional Verification of Digital Systems because it is not necessary to build a complex model, or use sophisticated techniques. Figure 1.2 shows the verification which is performed by means of simulation and formal verification of a digital system. The dynamic verification (based on simulation) uses a coverage model which represents a golden model because this contains all device functionality. This model is compared with the results obtained at the end of the simulation which are saved in the regression suit (where suit is a database). In every iteration a set of directed tests is produced by a test generator module using the information from the regression suit.

An important aspect of the Functional Verification is the functional coverage which can be defined as the percentage of verification objectives that have to be met. This is used as a metric for evaluating the progress of a verification project in order to reduce the number of simulation cycles expected in verifying a design. The coverage should be restricted to only those values that could indicate the design is fully verified. Also, the functional coverage is used to verify the correct operation of a device by means of the representation of a coverage model that contains one or more coverage points.

The coverage points are grouped in sets which are best known as coverage groups. A coverage group is a set of attributes, grouped together for purposes of deployment in a common

Figure 1.2. Functional Verification based on simulation vs Formal Verification.

correlation time. Also, a coverage group may contain different elements for different functions to verify the specification of a coverage model. These elements may include a clock event, a set of points, and weights for points, among others.

A functional coverage point can be a scalar value, a condition or an expression in a digital system. For example, the "output data" variable, since it is a variable that can take a set of values  $(0, 1, 2, ...2^n - 1)$ . These values are better known as *bins* (There is a glossary at the end the thesis). Examples of coverage points include: the level of occupancy of a buffer, an instruction code, address write/read in a memory, an input to a register, package longitude, etc. The objective of a coverage point is to ensure that all interesting and relevant values are observed in the sampled value or expression. Moreover, a coverage hole is a point which has not been exercised or tested during the functional process. After a device simulation it is important to analyze the produced information in order to review the exercised points and the holes that remain.

The coverage means the measure of the integrity of a test set. The coverage definition

represents the number of met goals by the test set which is used. Also, the functional coverage is defined as the number of defined goals which are met during the verification process.

During the verification process the verification engineers use a set of metrics in order to measure the validation process based on the simulation. At the beginning, they use basic metrics which require little effort, after that, they use more sophisticated metrics. A coverage metric can be defined as a parameter or attribute which is used as a unit in order to measure the verification process in one dimension. There are different kinds of metrics: code coverage, jump coverage, trajectory coverage, sentences coverage, etc. In the next subsection some aspects about functional verification are described.

#### **1.1.1 Elements of Functional Verification**

When Functional Verification for digital systems is performed, different elements are involved. These elements include: A functional specification, a verification plan, the implementation of the device, among others. A functional specification is the common source for the implementation and the verification of a device. Generally, it is implemented in two different documents with different abstraction levels:

- 1) The first one describes the requirements of the architecture to be implemented. It details the functions to be met by the device.

- 2) The second one is the specification of the device implementation. It describes the implementation of the device architect in a blocks level.

A verification plan is what will be verified and how to collect the verification information. It defines what should be verified and how it should be verified. Moreover, it describes the scope of the verification problem and is used as a functional specification for the test environment.

The device implementation is the design in a register transference level *RTL*, which is modeled in some hardware description language *HDL*. It is based on the specification according to the constraints and the prevision produced by the design engineer.

Different from software, where only the code sentences need to be verified, the hardware designs need to meet the specific times in order to perform the required functionally. Due to this, it is necessary to implement the design in a temporal modeling language.

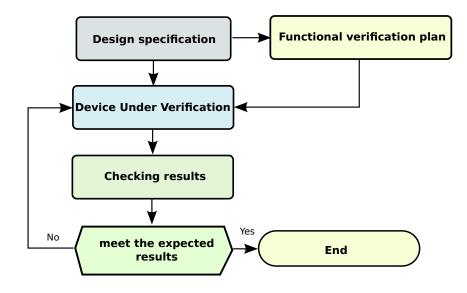

Figure 1.3 shows the flowchart of a general methodology in order to perform the functional device verification. The methodology of the functional coverage starts by the revision of the specifications of the digital system; after that, the implementation is performed. In order

to perform the Functional Verification, a coverage model is proposed. Given the model, a verification plan is necessary. After the simulation is performed, the results are checked and if a coverage percentage is reached, the process finishes or the test sequence is modified and is used once more.

Figure 1.3. General methodology for the functional verification process.

#### **1.2 Problem to Solve**

An important area for faults coverage is the Directed Functional Verification. Typically in industry, the digital systems have a set of conditions which should be met. In many environments of industrial designs, the verification engineers are not required to write the formal proprieties in order to prove that the behavior of the system is true. However, test sequences are required to search for errors and exercise the design functionality during the performed process in order to meet all required conditions.

The Directed functional verification performs an important role in order to meet the conditions of the functional specification. Due to the inconsistency of the pseudo-random

test generation methods in order to cover the hard cases, the engineers do not know the requirements of the Directed Functional Verification through simulation, especially with strict market requirements.

Different criteria in order to perform the functional tests generation of a digital system are needed because exhaustive search in a device of small size can require an exorbitant number of test vectors. An example is given in [1] and it is as follows: Given a device which has N inputs and M flip-flops,  $(2^N)^M$  vectors can be needed in order to perform the full functional verification. A modest size of a device can have 10 inputs and 100 flip-flops (around 3 registers of 32 bits). This device could require  $(2^{10})^{100}$  or  $2^{1000}$  for the full verification. It means if we perform the Functional Verification using 1000 test vectors by second, this can require 339, 540, 588, 380, 062, 907, 492, 466, 172, 668, 391, 072, 376,037, 725, 725, 208, 993, 588, 689, 808, 600, 264, 389, 893, 757, 743, 339, 953, 988, 988, 382, 771, 724, 040, 525, 133, 303, 203, 524, 078, 771, 892, 395, 266, 266, 335, 942, 544, 299, 458, 056, 845, 215, 567, 848, 460, 205, 301, 551, 551, 163, 124, 606, 262, 994, 092, 425, 972, 759, 467, 835, 103, 001, 336, 336, 717, 048, 865, 167, 147, 297, 613, 428, 902, 897, 465, 679, 093, 821, 821, 978, 784, 398, 755, 534, 655, 038, 141, 450, 059, 156, 501 years for the exhaustive test. The functional requirements should be exhaustively tested through formal methods.

In this research the problem to solve consists in finding test binary vector sequences which maximize the functional coverage percentage in a digital system of regular size. It can be defined as follows:

Given a binary space  $X = \{0, 1\}$  and a set of vectors  $T = \{\vec{t_1}, \vec{t_2}, ..., \vec{t_n}\}$  in order to verify a given digital system with a functional coverage B. The problem consists in finding a set of binary test sequences T' which maximizes B.

Where:  $\vec{t_i} \subseteq X, X \equiv \{0, 1\}^n$

Due to the increasing complexity of digital systems, the outperformance of the functional test generation based on the requirements (the functional specification) to be met is needed. Therefore, the problem to solve consists of proposing a method which produces the Directed Test Generation of test vector sequences in order to maximize the obtained coverage and reduce the time which is used to verify a digital system.

### 1.3 Justification

Currently, the cost of designing and manufacturing process of digital systems is greatly impacted by the step of verification and testing of such systems. Today, it is estimated that the cost of functional verification process involves between 60% and 70% of the total cost. Also, to perform the functional verification of digital systems is an open topic, since due to the high complexity of these systems, time and understanding of the temporary results of the progress of verification are required. That is, why does it take more efficient ways to perform the functional verification process?, and also, how to obtain high values of the total coverage percentage that is verified.

### **1.4 General Objective**

To propose a new test vector generation method in order to generate optimal functional coverages in the Functional Verification of Digital Systems using hardware simulation and metaheuristic algorithms.

#### **1.4.1** Specific Objectives

- 1.-To design and build a software platform in order to perform the functional verification of Digital Systems.

- 2.-To design a module in order to configure the different strategies of the test vectors generation.

- 3.- To design a new binary compact meta-heuristic algorithm in order to maximize the functional coverage.

- 4.- To compare meta-heuristic algorithms (GA, PSO, Compact-BinDE) and analyze the obtained results.

- 5.- To propose and solve the different optimization problems involved in the generation of optimal coverages for the different digital systems to be verified.

### 1.5 Research and developed method

The methodology which is used in this research is composed of the following steps:

- To perform the study of the state of the art related.

- To review the specification of digital systems to be tested.

- To analyze the implementation of the design at RTL level (VHDL, Verilog, SystemVerilog).

- To generate a verification plan based on the device to be tested.

- To propose functional coverage models based on the functional specification.

- To propose a heuristic criteria in order to perform the directed functional verification.

- To make the Directed Functional Verification of the digital systems based on a software tool.

- To analyze the obtained results and measure the advance of the functional coverage which is reached.

- To propose modifications of the verification process based on the obtained advances and the digital system which is tested.

#### **1.6** Scope of work

This research develops an automatic verification method in order to perform Directed Functional Verification of digital systems of medium size (ip core bus UART and FIFO memory) that obtain high coverage percentages based on the exercise of most of coverage points from the functional coverage models.

### 1.7 Contributions

An improved methodology in order to verify the functionality of digital systems based on a hybrid method (meta-heuristic and dynamic methods) which outperforms the original designs based on the verification.

**A hybrid method** which performs the Directed Test Vector Generation based on metaheuristic algorithms, coverage models and cost functions.

**The application** for first time of compact meta-heuristics to the Directed Functional Verification.

A new schema in order to generate optimal functional coverage in digital systems.

### 1.8 Organization

- **Chapter 1:** The fundamentals of this research are described. These are: Introduction, Problem statement, justification, the main objective and specific objectives, the methodology, the scopes and the contributions.

- **Chapter 2:** Different techniques and methodologies which have been used in order to perform the functional verification of digital systems are given.

- Chapter 3: The main definitions about the functional verification area are presented. Moreover, a background is mentioned. Among these definitions are: functional coverage, coverage metric, coverage models, etc.

- Chapter 4: The meta-heuristics background on the binary space is highlighted.

- Chapter 5: The architecture of the proposed system and the proposed method are described.

- Chapter 6: The experiments and obtained results based on the proposed method are shown and analyzed.

- Conclusions and future work are presented according to the obtained results and the development shown in the last chapters.

### 1.9 Resume