# **INSTITUTO POLITECNICO NACIONAL**

\_\_\_\_\_

# **CENTRO DE INVESTIGACION EN COMPUTACION**

Planificación de Tareas de Tiempo Real con Restricciones de Precedencia y Potencia

TESIS

QUE PARA OBTENER EL GRADO DE DOCTOR EN CIENCIAS DE LA COMPUTACION

PRESENTA

M. en C. Héctor Eduardo Silva López

DIRECTOR DR. SERGIO SUAREZ GUERRA

MEXICO, D.F.

Diciembre de 2009

## **AGRADECIMIENTOS**

Al Instituto Politécnico Nacional por su apoyo económico a través del programa de becas PIFI e Institucional.

Un agradecimiento especial a mí asesor, el Dr. Sergio Suarez Guerra, por el tiempo y esfuerzo dedicado durante todo este tiempo como director de esta tesis doctoral. Sin duda alguna, sus consejos y motivación han sido determinantes para el buen fin del mismo.

A los doctores del Centro de Investigación en Computación por compartir su entusiasmo por el conocimiento y ser participes de mi vida académica, en especial a los doctores: Dr. Sergio Suarez y el Dr. Juan Carlos Chimal.

A los miembros del jurado integrado por los siguientes: Dr. Luis Pastor Sánchez Fernández, Dr. Carlos Aguilar Ibáñez, Dr. Sergio Suárez Guerra, Dr. Pedro Guevara López, Dr. Marcelino Becerril Silva y el Dr. José de Jesús Medel Juárez, por sus incontables sugerencias y sobre todo por el tiempo dedicado en llevar al termino la presente tesis.

A todas las personas que integran la UTE, en especial a la Sra. Silvia Arteaga por todos los tramites que tuvo que realizar para que fuera acreedor a la beca PIFI e Institucional. A la Sra. Carmen Pitayo por todos los trámites administrativos que realizo y finalmente a la Maestra Martha Duran por todo el apoyo recibido desde mi ingreso hasta el día de mi graduación.

A mi querida esposa María del Pilar López Cárdenas, por haber iniciado esta aventura junto a mí, por su paciencia, por su comprensión y sobre todo por estar ahí cuando la necesitaba.

A mis hijos Abril y Alan por pasar los fines de semana sin salir de casa sin ningún reclamo y apoyándome en todo momento.

# **INDICE GENERAL**

| INDICE GENERAL                              | i   |

|---------------------------------------------|-----|

| LISTA DE FIGURAS                            | iv  |

| LISTA DE TABLAS                             | vi  |

| GLOSARIO DE TERMINOS                        | vii |

| CAPÍTULO 1.                                 |     |

| INTRODUCCIÓN.                               | 1   |

| 1.1 Factor de utilización.                  | 5   |

| 1.2 Planificación de tareas de tiempo real. | 5   |

| 1.3 Algoritmos de planificación.            | 7   |

| 1.4 Modelo del sistema.                     | 11  |

| 1.5 Motivación.                             | 13  |

| 1.6 Planteamiento del problema.             | 14  |

| 1.7 Hipótesis.                              | 14  |

| 1.8 Objetivos.                              | 15  |

| 1.8.1 Objetivo general.                     | 15  |

| 1.8.2 Objetivos específicos.                | 15  |

| 1.9 Justificación.                          | 16  |

| 1.10 Limitaciones y alcances.               | 17  |

| 1.11 Contribuciones de este trabajo         | 18  |

| Resumen.                                    | 19  |

| CAPÍTULO 2.                                 |     |

| ESTADO DEL ARTE                             | 20  |

| 2.1 Motivación.                             | 21  |

| 2.2 Consumo de potencia en dispositivos.    | 22  |

| 2.3 Tecnología de Baterías.                 | 23  |

| 2.3.1 Tecnología futura.                            | 28 |

|-----------------------------------------------------|----|

| 2.4 Arquitectura para el ahorro de energía.         | 29 |

| 2.5 Manejo de potencia en el procesador Core 2 Duo. | 32 |

| 2.5.1 Análisis de la arquitectura.                  | 33 |

| 2.5.2 Administración de energía.                    | 39 |

| 2.6 Consumo de energía en sistemas operativos.      | 42 |

| 2.7 Técnicas para el ahorro de energía.             | 43 |

| 2.8 Manejo de potencia.                             | 46 |

| 2.9 Procesadores de velocidad variada.              | 47 |

| 2.9.1 Procesador Intel Xscale                       | 47 |

| 2.10 Porcentaje de ahorro de energía                | 52 |

| Resumen.                                            | 55 |

|                                                     |    |

| CAPÍTULO 3.                                         |    |

| FORMULACIÓN DEL PROBLEMA.                           | 56 |

| 3.1 Problema de cálculo de variaciones.             | 56 |

| 3.1.1 Solución.                                     | 57 |

| 3.1.2 Algoritmo inicio.                             | 57 |

| 3.1.3 Algoritmo PD-N.                               | 58 |

| 3.1.4 Ejemplo del algoritmo.                        | 63 |

| 3.1.4.1 Inicio.                                     | 63 |

| 3.1.4.2 Desarrollo.                                 | 65 |

| 3.2 Programa lineal.                                | 67 |

| 3.2.1 Problema LBKP.                                | 68 |

| 3.2.2 Solución al KP-B.                             | 69 |

| 3.2.3 Ejemplo del algoritmo.                        | 70 |

| 3.2.3.1 Inicio.                                     | 71 |

| 3.2.3.2 Desarrollo.                                 | 71 |

| 3.3 Problema específico.                            | 72 |

| 3.3.1 Eiemplo del algoritmo.                        | 73 |

| Resumen.                                   | 77  |

|--------------------------------------------|-----|

| CAPÍTULO 4.                                |     |

| RESULTADOS.                                | 78  |

| 4.1 Resultado del apartado 3.1.            | 78  |

| 4.2 Resultado del apartado 3.2.            | 82  |

| 4.2.1 Discusión de resultados.             | 87  |

| 4.3 Resultado del apartado 3.3.            | 88  |

| Resumen.                                   | 93  |

| CAPÍTULO 5.                                |     |

| CONCLUSIONES.                              | 94  |

| 5.1 Conclusión del cálculo de variaciones. | 94  |

| 5.2 Conclusión de la programación lineal.  | 95  |

| 5.3 Conclusión del problema específico.    | 96  |

| 5.4 Aportaciones                           | 96  |

| 5.5 Trabajo a futuro                       | 97  |

| 5.6 Publicaciones                          | 98  |

| REFERENCIAS BIBLIOGRAFÍCAS.                | 100 |

| APENDICES.                                 |     |

| A: Definición de Sistema.                  | 108 |

| Estado de un proceso.                      | 108 |

| Tipos de restricciones de tareas.          | 109 |

| B: Multiprocesadores.                      | 116 |

| C: Servidor de láminas.                    | 119 |

| D: Procesamiento de imágenes.              | 121 |

# LISTA DE FIGURAS

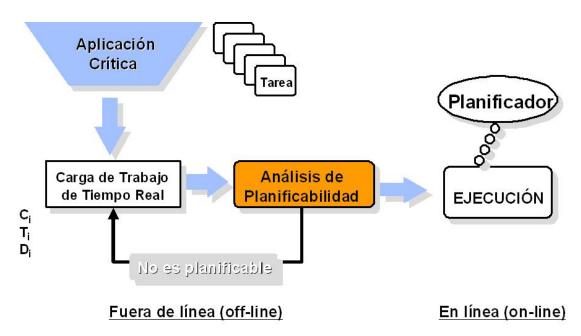

| Figura 1.1 Proceso de planificación.                                     | 7    |

|--------------------------------------------------------------------------|------|

| Figura 1.2 Justificación.                                                | 17   |

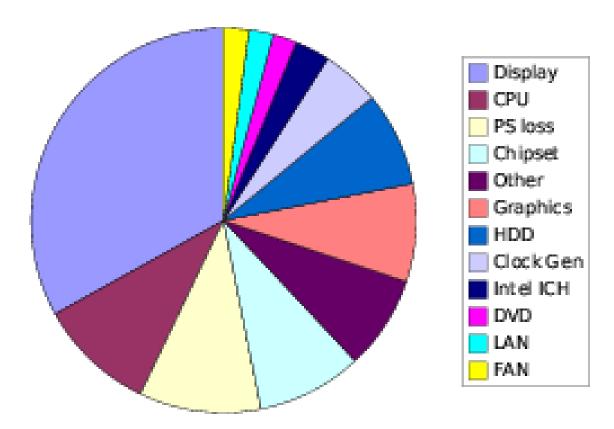

| Figura 2.1 Consumo de potencia en los dispositivos.                      | 23   |

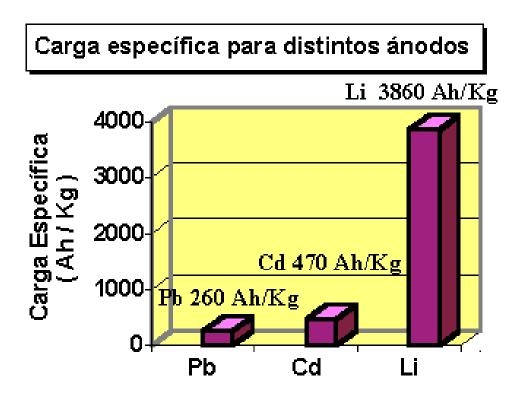

| Figura 2.2 Capacidad especifica.                                         | 25   |

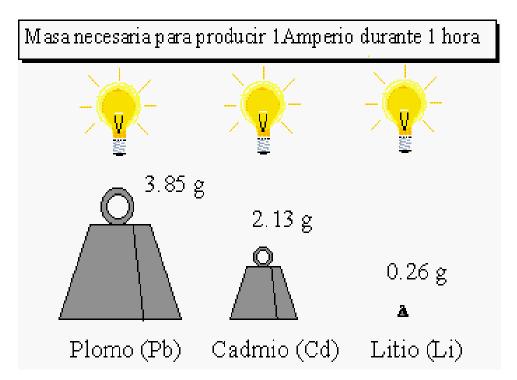

| Figura 2.3 Masa necesaria.                                               | 26   |

| Figura 2.4 Complejidad del diseño.                                       | 34   |

| Figura 2.5 Arquitectura de la capacidad de potencia inteligente.         | 37   |

| Figura 2.6 Nivel de abstracción.                                         | 38   |

| Figura 2.7 Consumo de potencia en estado desocupado.                     | 42   |

| Figura 2.8 Consumo de energía con carga.                                 | 43   |

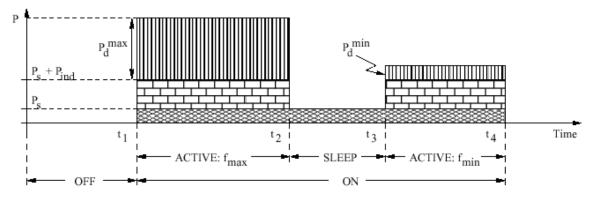

| Figura 2.9 Modelo de potencia sencillo: consumo de potencia en           | 50   |

| diferentes estados.                                                      |      |

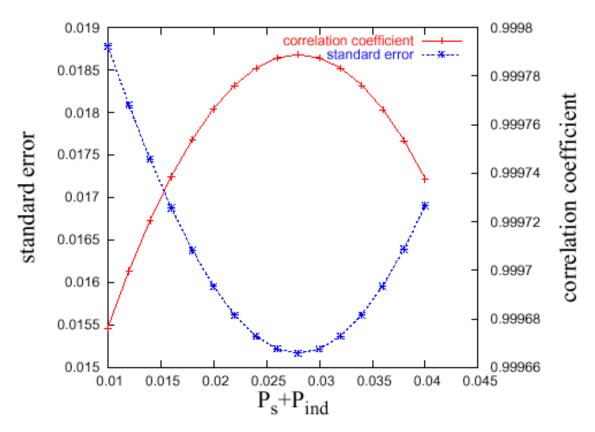

| Figura 2.10 Los errores estándares y los coeficientes de correlación par | a 53 |

| diferentes valores de $P_s + P_{ind}$ cuando se ajustan la potencia y la |      |

| frecuencia del procesador Intel XScale.                                  |      |

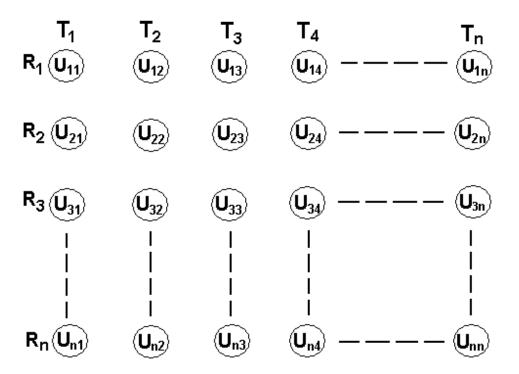

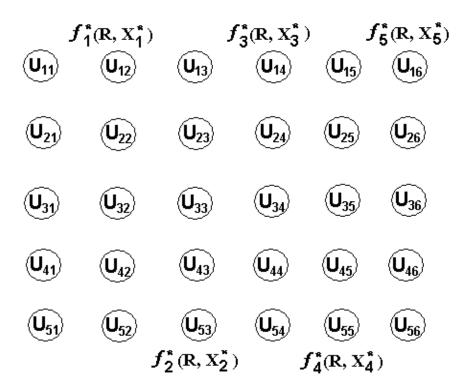

| Figura 3.1 Diagrama de estados de N etapas.                              | 59   |

| Figura 3.2 Ejemplo del diagrama de estados.                              | 61   |

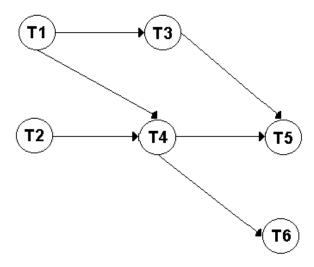

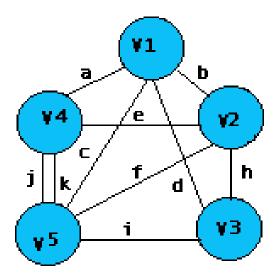

| Figura 3.3 Conjunto de tareas (DAG).                                     | 64   |

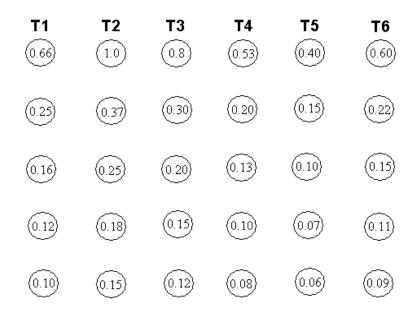

| Figura 3.4 Utilizaciones por estados.                                    | 66   |

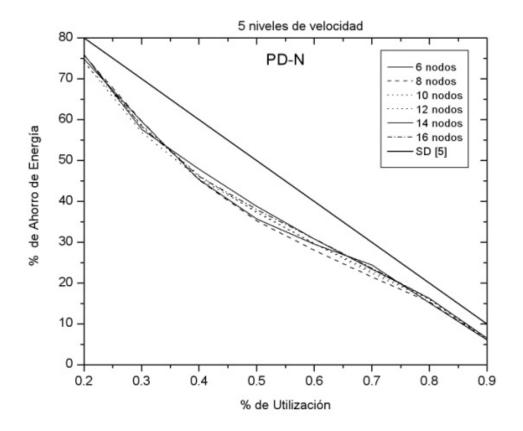

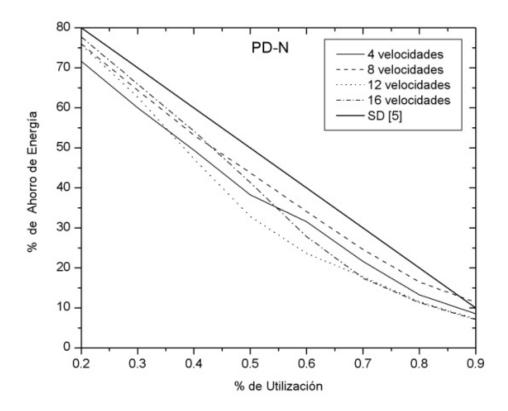

| Figura 4.1 % de S <sub>ij</sub> ahorro al variar el # de nodos.          | 80   |

| Figura 4.2 % de S <sub>ij</sub> al variar las velocidades.               | 81   |

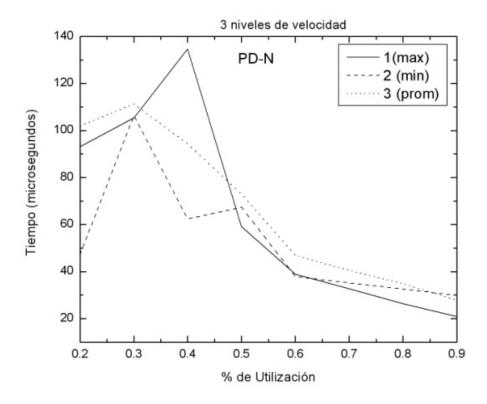

| Figura 4.3 Tiempo de ejecución para los tres métodos.                    | 82   |

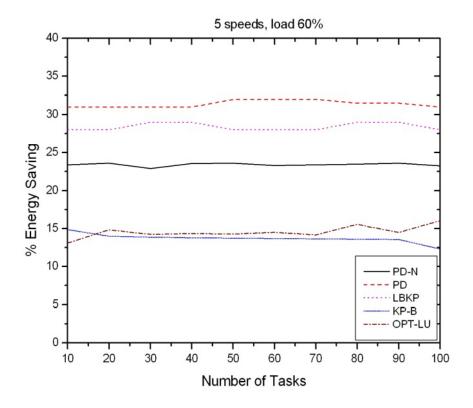

| Figura 4.4 Ahorro de energía                                             | 85   |

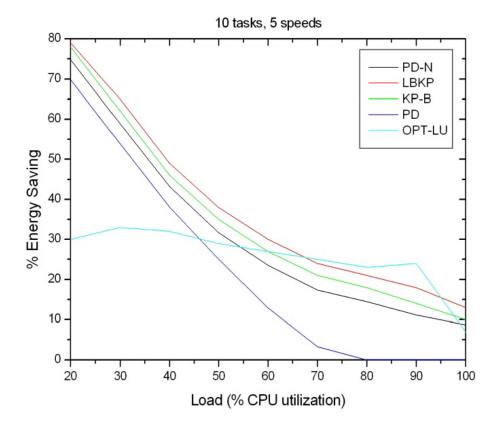

| Figura 4.5 Diferentes cargas de trabajo                                  | 86   |

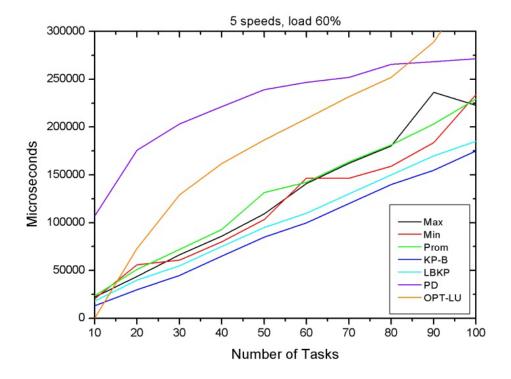

| Figura 4.6 Tiempo de ejecución                                           | 87   |

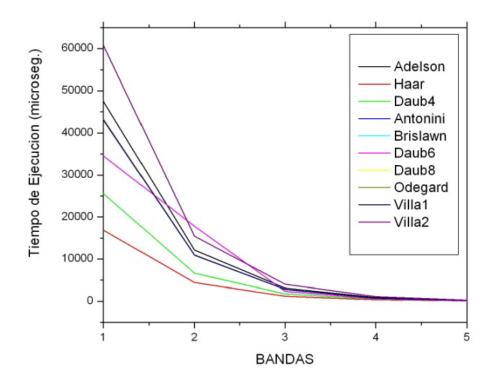

| Figura 4.7 Tiempo de ejecución para diferentes filtros                   | 89   |

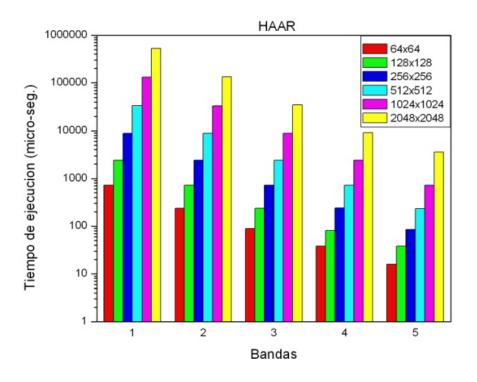

| Figura 4.8 Tiempo de ejecución para el filtro Haar                       | 90   |

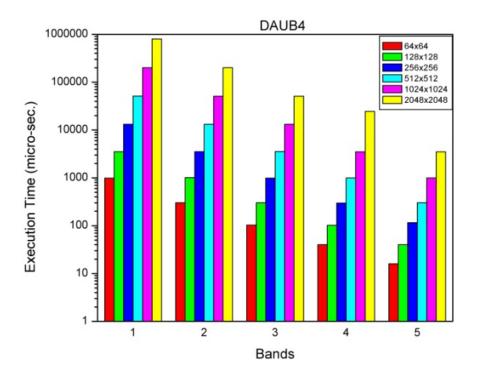

| Figura 4.9 Tiempo de ejecución para el filtro Daub4           | 90  |

|---------------------------------------------------------------|-----|

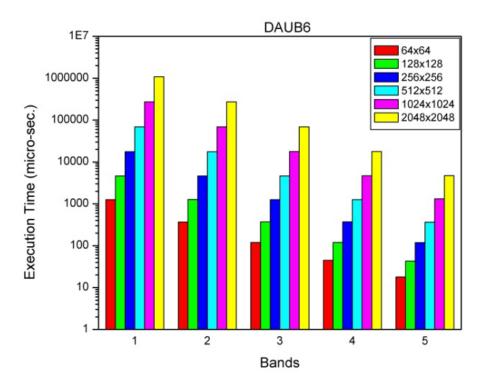

| Figura 4.10 Tiempo de ejecución para el filtro Daub6          | 91  |

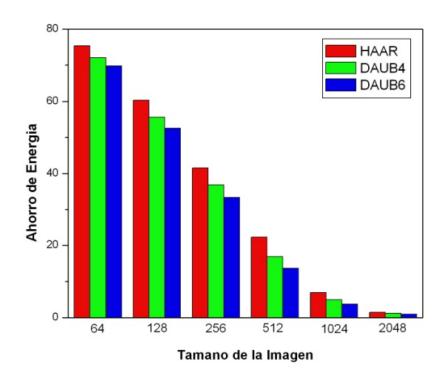

| Figura 4.11 Ahorro de energía a diferentes tamaños de imagen. | 92  |

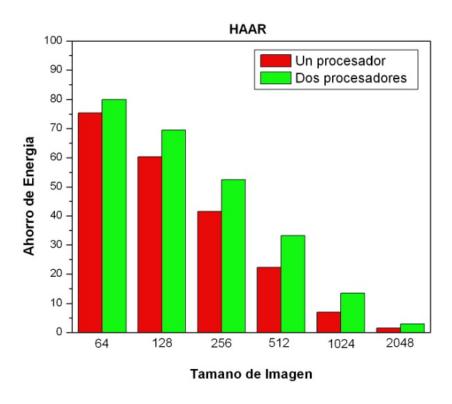

| Figura 4.12 Ahorro de energía para dos threads.               | 93  |

| Figura A.1 Diagrama de estado de un proceso.                  | 109 |

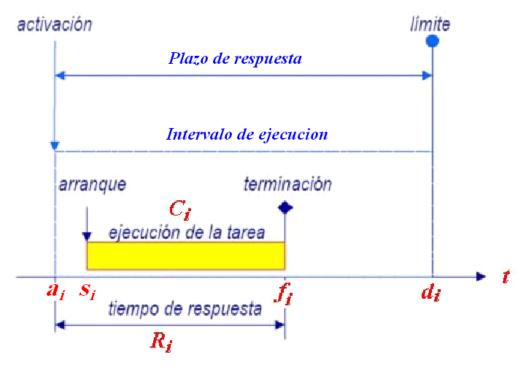

| Figura A.2 Requerimientos temporales.                         | 111 |

| Figura A.3 Grafo conexo.                                      | 113 |

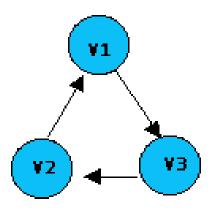

| Figura A.4 Grafo dirigido.                                    | 114 |

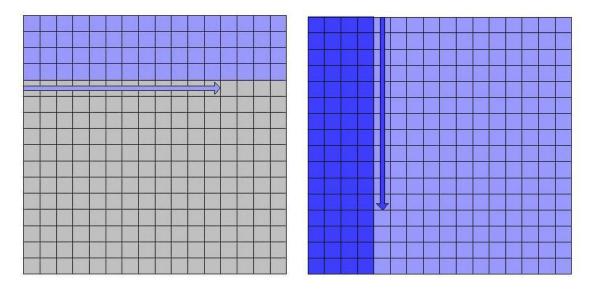

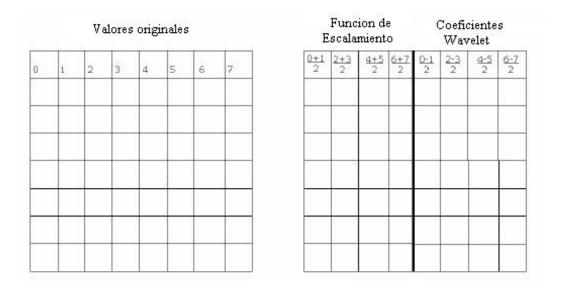

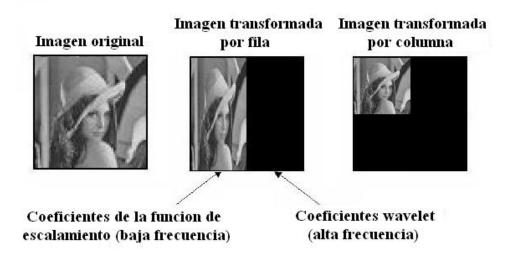

| Figura D.1 Transformada por fila y por columna.               | 123 |

| Figura D.2 Aplicación de la transformada wavelet.             | 124 |

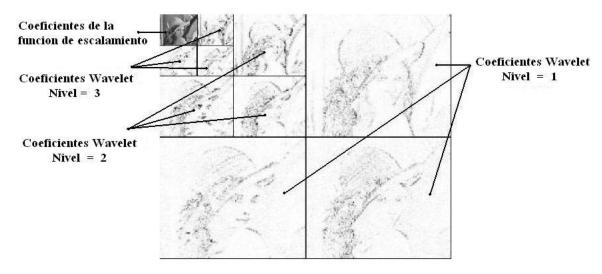

| Figura D.3 Transformada en el primer nivel.                   | 124 |

| Figura D.4 Transformada wavelet para tres niveles.            | 125 |

# LISTA DE TABLAS

| Tabla 2.1 | Velocidad y voltaje del Intel-XScale.                       | 51 |

|-----------|-------------------------------------------------------------|----|

| Tabla 2.2 | Porcentaje de ahorro de energía.                            | 54 |

| Tabla 3.1 | Restricciones temporales del DAG.                           | 64 |

| Tabla 3.2 | U <sub>ij</sub> y E <sub>ij</sub> a diferentes velocidades. | 65 |

| Tabla 3.3 | Resultados con los métodos.                                 | 67 |

| Tabla 3.4 | Primer paso.                                                | 71 |

| Tabla 3.5 | Segundo paso.                                               | 71 |

| Tabla 3.6 | Último paso.                                                | 72 |

| Tabla 3.7 | Utilización por sub-bandas                                  | 75 |

| Tabla 3.8 | Ahorro de energía por nivel                                 | 76 |

## **RESUMEN**

El problema que se presenta en esta tesis es la planificación de tareas de tiempo real con restricciones de precedencia y potencia con el objetivo de obtener el máximo ahorro de energía del conjunto de tareas y las sumas de las utilizaciones serán menores o iguales a la capacidad total del sistema. Para resolver esta cuestión se presenta el mismo como un problema de control óptimo en tiempo discreto, la metodología y dos algoritmos para resolverlo son implementados: el primero se resuelve como un problema de cálculo de variaciones y el segundo utiliza el método de la programación dinámica. Posteriormente se implementó un algoritmo específico para un problema en donde se maximiza la función objetivo propuesta.

El resultado para el primer algoritmo es el (PD-N) que tiene un buen desempeño al alcanzar un ahorro de energía muy cercana a la holgura en el sistema, para un número de nodos que van de 6 a 16 su comportamiento es muy parecido y muy cercano al óptimo, por último el tiempo de ejecución tiende a decrecer en cuanto la carga del procesador aumenta, pero una carga entre 0.2% y 0.5% vemos que el método Max emplea más tiempo de ejecución y el método Min el menor tiempo. El segundo algoritmo (KP-B) que se presenta como un problema de programación lineal con restricciones discretas, en donde la solución está basada en la ecuación de Bellman. Estos dos algoritmos se implementaron y se compararon con el más cercano de la literatura. Para el algoritmo KP-B el ahorro de energía, cuando se varía el número de tareas, es muy cercano al Opt-Lu. Cuando se varía la carga del procesador tiene un mejor ahorro de energía que el Opt-Lu a partir del 60% de carga del procesador. Con respecto al tiempo de ejecución el KP-B es el que tiene menor tiempo, estando dentro de los 13 y 175 milisegundos.

Y finalmente, el método y algoritmo específico que se implementó en una imagen obteniendo un ahorro de energía del 44.19%. En seguida se obtuvo el ahorro de energía para diferentes tamaños de imágenes, en donde los tamaños pequeños son los que presentan un ahorro de energía mayor y para un tamaño mayor se aprecia un ahorro de energía menor. Y finalmente se ejecutó el algoritmo en una ambiente de memoria compartida y se obtuvo un ahorro de energía promedio del orden de 28.77%.

## **ABSTRACT**

The problem presented in this thesis is real-time scheduling with precedence and power constraints in order that the energy saving of the system is maximized without having the utilization sum exceed the capacity of the system. To resolve this issue a discrete time optimal control problem is presented. A methodology and two algorithms for solving it are implemented: the first is solved as a calculus of variations problem and the second using the dynamic programming method. A specific algorithm was implemented where the proposed objective function is maximized.

The result of the first algorithm (PD-N) produced a good performance by achieving energy saving very close tolerance level in the system for a number of nodes ranging from 6 to 16; their behavior is very similar and very close to optimal. Finally the execution time tends to decrease as processor load increases, but a charge between 0.2% and 0.5% showed that the Max method uses more runtime and the Min method the shortest time. The second algorithm (KP-B) is presented as a discrete constraints linear programming problem, where the solution is based on the Bellman equation. The algorithms presented in this work were compared to those proposed in literature for solving this kind of problem. When the number of the tasks varied for the KP-B algorithm, the execution time was very close to that of Opt-Lu, and when the processor load varied, from 60% of processor load and upwards it had better energy saving that Opt-Lu. Regarding the execution time, the KP-B had the shortest, being between 13 and 175 milliseconds.

Finally, for the specific method an energy saving of the 44.19% is obtained for an image. Then energy saving for different image sizes was obtained, thus concluding that a grater energy saving occurs for small image sizes, whereas for bigger size, less energy is saved. Later, when executing the algorithm in a shared memory environment, an extra saving to the order of 28.77% on average was obtained.

## **CAPITULO 1**

## **INTRODUCCION**

En este capítulo como antecedentes, se presentan los conceptos básicos de un sistema de tiempo real, se explica el concepto de factor de utilización, así como se presentan los principales algoritmos de planificación. El modelo del sistema es en seguida mostrado, después lo que motivó el desarrollo de la presente tesis, luego se plantea el problema a resolver y por último los objetivos a desarrollar en este trabajo de tesis y su justificación, así como las limitaciones de la tesis y las contribuciones del trabajo.

El tiempo de respuesta de un sistema de software es el que transcurre entre que se ponen un conjunto de entradas al sistema y que aparecen todas las salidas asociadas del mismo.

Tradicionalmente se ha considerado que un sistema computacional funciona correctamente cuando la solución obtenida es correcta desde el punto de vista lógico. Esta definición, si bien es válida para sistemas de cálculo convencional, no es suficiente cuando estamos considerando sistemas que interactúan fuertemente con el entorno. Este tipo de sistemas, normalmente dedicados a tareas de monitoreo o control, suelen estar formados por un conjunto de recursos tales como sensores, unidades de cómputo y actuadores que deben trabajar de forma coordinada para realizar la labor encomendada. La cooperación entre diferentes recursos obliga, no sólo a que cada operación sea correcta, sino a que se realice en los instantes oportunos. Este tipo de sistemas a los que es preciso imponer restricciones temporales se les denominan sistemas de tiempo real [44, 61].

1

Existen las siguientes definiciones de un sistema de tiempo-real (STR).

- Laplante: Un sistema de tiempo real es un sistema cuyos tiempos de respuesta deben satisfacer requisitos explícitos, y que en caso de no responder dentro de acuerdo a los requisitos pueden producirse consecuencias graves, incluyendo el fracaso del sistema.

- ➤ Un STR *fracasa* si no puede satisfacer uno o más de los requisitos establecidos en la especificación del sistema.

#### Burns:

Un sistema de tiempo real es un sistema de procesamiento de información que debe responder a estímulos generados externamente dentro de un período finito y especificado.

- la correctitud depende no sólo del resultado lógico sino también del instante en que el sistema lo produce

- el no respeto de los requisitos temporales es tan malo como una respuesta incorrecta.

Las tareas de tiempo real se pueden clasificar en base a las consecuencias provocadas por la pérdida de los plazos de respuesta en los siguientes tipos:

- Sistemas de Tiempo Real duros. Sistemas en los que es absolutamente imperativo que las respuestas ocurran dentro de los períodos de tiempo especificados, a riesgo de causar un desastre. (Ej: Sistema de Control de Vuelo).

- 2. Sistemas de Tiempo Real Suaves. Sistemas en los cuales los requerimientos temporales son importantes, pero que igualmente funcionan correctamente si ocasionalmente los mismos no se respetan: el desempeño es degradado pero no se destruyen por el hecho de fracasar. (Ej: Sistema de Adquisición de Datos).

3. Sistemas de Tiempo Real Firmes. Son sistemas de tiempo real suaves, pero en caso de no respetar las restricciones de tiempo no sirve de nada el servicio que prestan.

Una Tarea de Tiempo Real es una entidad ejecutable  $J_i$  que al menos es caracterizada por un tiempo de arribo y una restricción temporal. Está formada por un conjunto de instancias  $J_k$ , tal que  $J_i = \{j_k\}$  con  $i,k \in \mathbb{Z}^+$ , [19].

Considerando la regularidad en la ejecución de las tareas de tiempo real, se pueden clasificar como:

- 1. *Tarea Periódica.-* Reiniciación periódica de tareas, cada instancia debe completar antes de su plazo.

- Tarea aperiódica.- Se activan al producirse determinados eventos de forma imprevisible. Se ejecutan sólo durante una instancia de ejecución al término de la cual desaparecen. Las tareas tienen plazos suaves o no tienen plazos.

- Tarea esporádica.- Son tareas aperiódicas con restricciones temporales críticas (o duras). Si se monitorea el arribo, es posible determinar una separación mínima entre activaciones consecutivas, lo cual podría permitir caracterizarlas como tareas periódicas.

Los sistemas de tiempo real son concurrentes por naturaleza. Un sistema concurrente se compone de un conjunto de procesos o *tareas* que se ejecutan de forma aparentemente paralela. Un sistema de tareas concurrentes en un solo procesador se puede ejecutar multiplexando el tiempo de varias formas:

- Ejecución síncrona: ejecutivo cíclico.

- > Ejecución asíncrona:

- Núcleo de multiprogramación separado (SO de tiempo real).

Lenguaje de programación concurrente.

Cuando se usa un lenguaje concurrente, el multiplexado del procesador se realiza por medio de un núcleo de ejecución *(run-time system)*.

Las características principales de los sistemas de tiempo real son:

- Oportunidad (timeliness): un STR debe operar de forma tal que satisfaga determinados requisitos de tiempo, que pueden ser de dos tipos:

- Requisitos de tiempo relativos: si una acción debe ocurrir dentro de un intervalo de tiempo dado relativo a la ocurrencia de un evento

- Requisitos de tiempo absolutos: si una acción debe ocurrir en un punto fijo de tiempo.

- Simultaneidad: un STR debe responder dentro de intervalos de tiempo predeterminado a los diferentes estímulos (eventualmente simultáneos) que reciba desde el exterior. Para satisfacer este requisito, debe operar en forma paralela (ya sea a través de procesadores múltiples o cuasi-paralelismo).

- Predictibilidad: un STR debe comportarse dentro de los límites que se derivan de su especificación; los resultados que produce un STR frente a determinados estímulos deben ser completamente predecibles.

- Confiabilidad (dependability), que implica:

- correctitud: el sistema se comporta de acuerdo a su especificación.

- robustez: el sistema permanece en un estado predecible, aún cuando el entorno no corresponda a las especificaciones.

- disponibilidad (readiness): los procesos de un STR consisten en un lazo infinito, a los efectos de interactuar continuamente con el entorno.

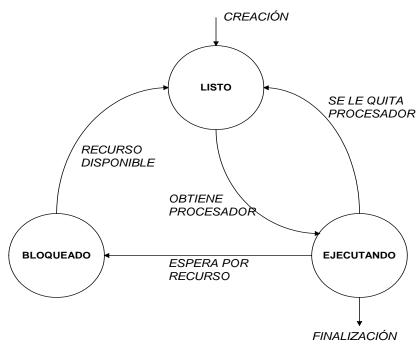

El estado de un proceso así como las restricciones de los sistemas de tiempo real, sé pueden consultar en el apéndice A.

#### 1.1 Factor de utilización.

Se considera un conjunto  $T=\{T_1,...,T_n\}$  de n tareas periódicas y desalojables de tiempo real, corriendo en un procesador. Cada tarea  $T_i$  está compuesta de restricciones de precedencia igual a un grafo. El periodo de  $T_i$  es representado por  $P_i$  (entero no negativo), el cual es igual al plazo de respuesta relativo de la tarea.  $C_i$  es un entero y representa el tiempo de ejecución requerido por  $T_i$ . El factor de utilización del procesador U es la fracción de tiempo consumido por el procesador en la ejecución del conjunto de tareas. Dado que  $C_i/P_i$  es la fracción de tiempo que consume el procesador en ejecutar la tarea  $T_i$ , el factor de utilización para n tareas está dado por:

$$U = \sum_{i=1}^{n} \frac{C_i}{P_i} \tag{1}$$

El factor de utilización provee una medición de la carga de trabajo ejecutándose en la CPU (Unidad Central de Procesamiento).

# 1.2 Planificación de tareas de tiempo real.

Para maximizar el número de tareas de tiempo-real que pueden ser procesadas sin violaciones, los sistemas computacionales de tiempo real usan sofisticados algoritmos de planificación para decidir el orden en el cual las tareas son ejecutadas. El desempeño de un algoritmo de planificación es medido por su habilidad para generar una planificación factible para un conjunto de tareas de tiempo real. Un planificador para asignar tareas a uno o más procesadores se dice que es factible si la ejecución de cada tarea puede ser completada antes del plazo de respuesta. Un planificador factible se dice ser mínimo si no hay una planificación factible utilizando menos procesadores. Un algoritmo de planificación

se dice ser óptimo, si para un conjunto de tareas, el algoritmo encuentra una planificación mínima.

Los algoritmos de planificación se clasifican en ocho clases principales y estos son:

- Desalojo: La tarea que está en ejecución puede ser interrumpida en cualquier momento para asignar al procesador otra tarea, siguiendo una política de planificación previamente establecida.

- Sin desalojo: Una vez asignada la tarea al procesador, ésta permanece en ejecución hasta que termina. Las decisiones de planificación son tomadas cuando la tarea termina.

- Estática: Las decisiones de planificación son tomadas antes que comiencen la activación de las tareas.

- Dinámica: Las decisiones de planificación son tomadas cuando las tareas se están ejecutando en forma dinámica.

- Fuera de línea: Las decisiones de planificación son tomadas antes de que se ejecuten las tareas. Estas decisiones son almacenadas en una tabla y después es ejecutada por un despachador.

- ➤ En línea: Las decisiones de planificación son tomadas en tiempo de ejecución cada vez que una tarea comience o termine su ejecución.

- Optima: Se dice óptimo si se minimiza alguna de las funciones de costo definidas sobre el conjunto de tareas. Cuando no es definida una función de costo, y lo único es alcanzar una planificación factible, entonces el algoritmo de planificación es óptimo si éste encuentra una solución de planificación que no pueda ser contradecida por ningún otro algoritmo de planificación. La solución indica si el conjunto de tareas es factible o no es factible (si cumple o no con sus plazos de respuesta).

- Heurístico: Encuentra una solución aproximada que intenta estar cerca de la solución óptima.

Los algoritmos de planificación pueden ser divididos dentro de: algoritmos de prioridad fija y algoritmos de prioridad dinámica. En los algoritmos de prioridad fija, la prioridad de una tarea permanece constante todo el tiempo, por otro lado en un algoritmo de prioridad dinámica, la prioridad de una tarea puede cambiar durante su ejecución. Estos algoritmos se pueden apreciar en la figura 1.1.

Figura 1.1. Proceso de planificación.

# 1.3 Algoritmos de planificación.

# **Monoprocesadores**

Liu y Layland dedujeron la primera prueba de planificabilidad dentro del algoritmo RMA [18]. Esta prueba se aplica al caso de que las n tareas sean independientes en su ejecución, con plazos de finalización iguales a sus períodos. Los autores probaron que la asignación de prioridades óptima para este tipo de sistemas era el Rate Monotonic Scheduling (RMS), que asignan mayor prioridad al que tiene menor periodo de activación. Esta asignación es óptima en el sentido de que si un sistema con esta asignación no es planificable, entonces no hay ninguna otra

asignación de prioridades que haga que el sistema lo sea. En estas condiciones, el sistema será planificable si cumple:

$$U = \sum_{i=1}^{n} \frac{C_i}{T_i} \le U(n) = n \left( 2^{\frac{1}{n}} - 1 \right)$$

(2)

Donde:

U - La utilización total del procesador.

U(n) - El límite de utilización máximo del procesador para n tareas.

Esta prueba condiciona la planificabilidad del sistema a que la utilización total del procesador no sobrepase un valor máximo establecido, dependiendo del número total de tareas. Este límite de utilización varia (para n>1) entre el 83% y el 69%, lo cual apunta a sistemas planificables para utilizaciones relativamente bajas. Esta prueba es suficiente pero no necesaria, de forma que puede haber conjuntos de tareas que sobrepasen el límite de utilización establecido por la prueba y que, sin embargo, sean planificables.

Lehoczky, Sha y Ding [39] propusieron una prueba exacta para este mismo caso. Para ello, valiéndose de la definición de instante critico, definen una utilización del peor caso para una tarea  $T_i$ , en un intervalo de anchura t. Esta utilización del peor caso se obtiene como la cantidad total de tiempo de ejecución requerida por tareas de prioridad mayor o igual que la de  $T_i$ , dividido entre la anchura t, es decir:

$$U_{i}(t) = \frac{\sum_{j=1}^{i} \left( \left\lceil \frac{t}{T_{j}} \right\rceil C_{j} \right)}{t}$$

(3)

Donde:

$U_i(t)$  - La utilización del peor caso en el intervalo (0,t).

$\lceil x \rceil$ - Función techo, definida como el menor entero mayor o igual que x.

Entonces, el sistema será planificable si se cumple:

$$\min_{0 < t < T_i} U_i(t) \le 1 \quad \forall i = 1...n \tag{4}$$

Cuando los plazos de finalización son menores que los períodos, las pruebas anteriores ya no son válidas. Además, la asignación de prioridades en función de los periodos ya no es óptima: Leung y Whitehead probaron que, en este caso, la asignación óptima es la basada en los plazos de ejecución (deadline monotonic, DM) [37], de forma que le corresponde la mayor prioridad a la tarea que tenga menor plazo de ejecución.

Audsley [4] desarrolló una prueba de planificabilidad suficiente, basado también en utilizaciones, para un conjunto de tareas con asignación de prioridades según sus plazos de ejecución. La mayor interferencia en la ejecución de una tarea  $T_i$  se produce en un instante crítico. Para una tarea que cumpla su plazo, esta interferencia está limitada por la expresión:

$$I_i = \sum_{j \in hp(i)} \left[ \frac{D_i}{T_j} \right] C_j \tag{5}$$

En donde:

hp(i).- Es el conjunto de tareas que pueden interferir la ejecución de  $T_i$ , formado por las tareas con prioridad mayor o igual que la de  $T_i$ , (exceptuando la propia  $T_i$ ).

El sistema será planificable si cada tarea experimenta una utilización máxima, definida dentro de su plazo, menor del 100%. Esto es:

$$\frac{C_i}{D_i} + \frac{I_i}{D_i} \le 1 \quad \forall i = 1...n$$

(6)

Esta prueba no es exacta, ya que supone que las tareas de mayor prioridad del conjunto hp(i) pueden interrumpir la ejecución de  $T_i$  en cualquier instante dentro

del plazo, sin tener en cuenta que la ejecución de  $T_i$  podría haber finalizado antes de que esa expulsión se hubiera producido.

Todas las pruebas que se han presentado se basan en la utilización del procesador y nos permiten estudiar la planificabilidad de sistemas con asignación de prioridad Rate Monotonic y Deadline Monotonic. Un método más potente, en el sentido de que permite estudiar conjuntos de tareas con plazos menores o iguales que el sentido de que permite estudiar conjuntos de tareas con plazos menores o iguales que el periodo y cualquier asignación arbitraria de prioridades, es el desarrollado por Joseph y Pandya [34]. Este método es equivalente al algoritmo de Dilatación Temporal (Time Dilation Algorithm) desarrollado por Harter [23] y que utiliza lógica temporal para obtener tiempos de respuesta. El método de Joseph y Pandya se basa en el cálculo de los tiempos de respuesta peor caso de cada tarea. Si Ri es el tiempo de respuesta del peor caso de una tarea  $T_i$ , la máxima interferencia producida a partir del instante crítico, debida a tareas de mayor prioridad viene dada por:

$$I_{i} = \sum_{j \in hp(i)} \left\lceil \frac{R_{i}}{T_{j}} \right\rceil C_{j} \tag{7}$$

El tiempo de respuesta del peor caso *Ri* vendrá dado por la suma de esta interferencia más el tiempo de ejecución de la propia tarea, esto es:

$$R_i = C_i + I_i \tag{8}$$

De forma que la planificación del sistema se condiciona a que se cumpla

$$R_i \le D_i, \quad \forall i = 1...n$$

(9)

En sistemas de tiempo real estricto si es imprescindible que nunca se pierdan los plazos de ejecución; esto quiere decir, que una prueba válida para el análisis de planificabilidad debe ser siempre suficiente. Por otra parte, una prueba que no sea exacta será aceptable cuanto más se acerque para cumplir con los plazos de respuesta.

El algoritmo EDF (Earliest Deadline First) propuesto por [18, 44], asigna las prioridades a las tareas dependiendo de la cercanía del plazo de respuesta; la tarea con el plazo más cercano recibe la prioridad más alta. En cualquier instante, la tarea con más alta prioridad puede desalojar a la tarea que en ese momento utilice el procesador. La condición necesaria y suficiente para planificar un conjunto de tareas bajo EDF es:

$$\sum_{i=1}^{n} \binom{C_i}{P_i} \le 1 \tag{10}$$

Donde n es el número total de tareas.

El algoritmo EDF es óptimo en el sentido de que si un conjunto de tareas es factiblemente planificado por cualquier algoritmo de planificación de prioridades dinámicas, entonces también es planificado bajo EDF. Algoritmos con manejo de prioridad dinámica tienen cierta ventaja sobre los algoritmos de prioridad fija. Una ventaja de este algoritmo, radica en el hecho de que la cota límite es (máxima) 100% para cualquier conjunto de tareas. Esto significa que el CPU puede ser utilizado totalmente. La principal desventaja de EDF se encuentra en que no existe una manera de identificar que tareas perderán sus plazos de respuesta ante un evento de sobrecarga  $(\sum_{i=1}^n (C_i/P_i > 1))$  ocurre.

## Multiprocesadores.

En el apéndice B se presenta el estado en los sistemas multiprocesadores.

#### 1.4 Modelo del sistema.

Generalmente un problema de planificación se define por cuatro parámetros: a) El ambiente del sistema, b) La caracterización de las tareas, c) El ambiente de planificación, y d) Los objetivos de planificación. El ambiente del sistema

especifica los tipos de procesadores a utilizar. Se dice que los procesadores son homogéneos si la ejecución de una tarea en particular sobre cualquier procesador toma el mismo tiempo de cómputo (capacidad de procesamiento, acceso a memoria y acceso a dispositivos de entrada y salidas), además se considera que los procesadores son heterogéneos. La caracterización de las tareas permite especificar las restricciones de tiempos de las tareas, las relaciones y jerarquías entre ellas. El ambiente de planificación describe las restricciones impuestas sobre el algoritmo de planificación: si las tareas son desalojables o no; si la planificación se lleva a cabo en un esquema en línea o fuera de línea. Finalmente los objetivos nos definen las metas a alcanzar: reducir el número de procesadores, lograr que todas las tareas cumplan sus plazos, minimizar el tiempo de cómputo, etc. Considerando estos puntos, para nuestro estudio asumiremos las siguientes condiciones:

- a) Para el ambiente del sistema, se consideran un procesador y el sistema operativo a utilizar (Linux).

- b) Para la caracterización de las tareas  $T_i$ , se consideran a éstas con restricciones de precedencia y restricciones de potencia. Los parámetros a que definen a una tarea son, el tiempo de ejecución,  $C_i$ , el periodo  $P_i$ y el plazo de respuesta  $D_i$ . Se consideran sólo tareas periódicas, es decir, que su arribo se realiza a intervalos de tiempo de duración fija y asumiremos que el plazo de respuesta de una tarea corresponde a su siguiente tiempo de arribo (o periodo). El periodo y el tiempo de cómputo de la tarea  $T_i$  satisface que  $T_i > 0$  y  $0 \le C_i \le T_i = D_i, (i = 1,...,n)$ . Así mismo se define  $u_i = C_i/T_i$  como el factor de utilización de la i-esima tarea. El factor de utilización del conjunto de tareas es la suma de los factores de utilización de las tareas en el conjunto,

$$U_T = \sum_{i=1}^n \frac{C_i}{T_i} \tag{11}$$

- c) Para el ambiente de planificación, se asume que las tareas pueden ser desalojadas en cualquier momento, es decir, en cierto instante el despachador determina que tarea va a ejecutar. El costo del desalojo y arribo de una tarea se considera nulo. Las tareas no requieren un acceso exclusivo a otro recurso más que al procesador. Se utiliza un esquema de asignación de prioridad de acuerdo a la función de objetivo y a las restricciones impuestas y se lleva a cabo siguiendo un orden de prioridad decreciente. Esto es, siempre se ejecutará primero la tarea con la más alta prioridad de todas las que han arribado. Otro parámetro en el ambiente de planificación, es aquel relacionado con las características del conjunto completo de tareas. En este caso, consideramos a la planificación fuera de línea (off-line) así como a la planificación en línea (on-line).

- d) Los objetivos de planificación son I) Que todos los plazos de respuesta de las tareas se cumplan, II) Minimizar el consumo de energía o maximizar el ahorro de energía de acuerdo a las restricciones de precedencia y restricciones de potencia del conjunto de tareas de tiempo real.

#### 1.5 Motivación.

Con el advenimiento de los sistemas de cómputo portátiles y de tamaño pequeño, incluyendo la nueva tendencia de los sistemas en un solo chip, el consumo de potencia ha emergido recientemente como el punto principal en muchos proyectos de investigación y de los sistemas comerciales. Estos proyectos típicamente direccionan su objetivo en minimizar el consumo de potencia en una plataforma dada, la cual puede ser transportada con la ayuda de una batería de larga duración. Actualmente los sistemas con una potencia eficiente manejan funciones que pueden ser invocadas para apagar algunos componentes del sistema o

pueden escoger entre diferentes estados para cada componente. El Manejo de Potencia Avanzado (Advance Power Management, APM) y la Interfaz de Potencia y la Configuración Avanzada (Advanced Configuration & Power Interface, ACPI) son interfaces estándar que proveen las aplicaciones con alguna funcionalidad para el manejo de potencia. Recientemente la investigación ha demostrado que más allá de la reducción en el consumo de potencia, ésto puede ser acompañado por un escalamiento dinámico del voltaje/frecuencia, éstas pueden ser técnicas de un compilador y poder seleccionar el uso alternativo de algoritmos

# 1.6 Planteamiento del problema.

Se considera un sistema de tiempo real en el cual todas las tareas son periódicas. Cada instancia se le denominará como sub-tarea y existirán un número finito de instancias, las cuales deberán ser ejecutadas antes del siguiente arribo de la próxima tarea. En su estado inicial todas las tareas estarán a su máximo nivel de velocidad. El conjunto de tareas estará representado por un Grafo acíclico dirigido (DAG en inglés) así que cada vez que arribe o salga un DAG del sistema, el problema es determinar el modo (velocidad del procesador) de ejecución de las tareas (o nodos en el grafo), tal que no se pierdan sus plazos de respuesta y el ahorro de energía del sistema sea maximizado. Todas las tareas tendrán un número finito de modos de ejecución, donde se escogerá un modo para su ejecución. Notar que la solución a este problema deberá ser calculado cada vez que una tarea arribe o salga del sistema, además una solución con una alta complejidad computacional puede ocasionar probablemente que se pierdan los plazos de respuesta. Esto significa que la solución requiere un algoritmo con un resultado eficiente de bajo costo computacional. Las soluciones heurísticas se caracterizan por tener esta propiedad.

## 1.7 Hipótesis.

En un STR las tareas que se ejecutan en cada hiperperíodo pueden variar en cantidad y por tanto en sus características, lo que obliga a re-planificar el sistema cada vez que hay cambio de tareas. Existe la posibilidad de realizar una planificación en función del hiperperíodo total y adecuar las velocidades de ejecución de las tareas, para lograr un ahorro general de energía en el consumo del sistema.

## 1.8 Objetivos.

El objetivo de investigación es encontrar una nueva solución al problema de la planificación de tareas de tiempo real con restricciones de precedencia y restricciones de potencia. Con la finalidad de poder minimizar el consumo de potencia conservando las restricciones temporales de las tareas, es decir, que las tareas se ejecuten dentro de sus plazos de respuesta.

# 1.8.1 Objetivo general.

Planificar un conjunto de tareas de tiempo real concurrentes con restricciones de precedencia y potencia con la finalidad de maximizar el ahorro de energía.

Se utilizará, la metodología de optimización de sistemas dinámicos, es decir, la optimización de sistemas que evolucionan en el tiempo, se proponen algoritmos para su implementación.

## 1.8.2 Objetivos específicos.

Realizar la modelación matemática a través de una estructura discreta o combinatoria.

- Calcular la complejidad computacional del problema matemático surgido de la modelación.

- Presentar el algoritmo que se usará para encontrar la solución al problema en cuestión.

- Proponer una solución al presentarlo como un problema de cálculo de variaciones el cual es resuelto como un problema de control optimo en tiempo discreto.

- Resolver el problema planteado como un problema de control óptimo en tiempo discreto, utilizando el método de la programación dinámica

- Implementar un algoritmo específico para un problema específico en donde se maximicé la función objetivo propuesta.

#### 1.9 Justificación.

En la figura 1.2 se aprecia cómo se encuentra el estado del arte para los sistemas de tiempo real utilizando tareas periódicas concurrentes y ejecutándose en un ambiente con un solo procesador. El considerar tareas periódicas de tiempo real con restricciones de precedencia y potencia no ha sido considerado y nadie hasta el momento ha presentado algo en esta área. Por esta razón se está proponiendo precisamente esta situación y es la de presentar una metodología con su algoritmo de optimización para tratar a las tareas periódicas con restricciones de precedencia y restricciones de potencia utilizando un procesador, con el objetivo de maximizar el ahorro de energía de los sistemas de tiempo real.

Figura 1.2. Justificación.

# 1.10 Limitaciones y alcances.

Las limitaciones y alcances de la presente tesis, son las siguientes:

- La implementación de los algoritmos propuestos en esta tesis son únicamente probados en un ambiente de simulación. En una Laptop convencional y utilizando alguna versión libre del sistema operativo Linux.

- 2. La simulación consiste en igualar un ambiente de un sistema operativo de tiempo real, para contar con todas los atributos de las tareas de tiempo real.

- 3. La simulación también cuenta con todas las características de un procesador de velocidad variable, con cambios discretos de velocidad.

- 4. Los algoritmos propuestos por otros autores en la literatura, son adaptados al sistema de simulación desarrollado.

- 5. Los resultados obtenidos en la simulación son graficados utilizando un software comercial (Origin versión 7.5).

- 6. Las ecuaciones utilizadas para obtener el porcentaje del ahorro de energía, así como para el consumo de potencia son las presentadas por los fabricantes de procesadores de velocidad variable y en ningún momento se modifican o se desarrollan nuevas ecuaciones.

- 7. Para calcular la utilización de cada tarea a cada velocidad, se usa la que se utiliza en la literatura referida en su momento. Y no se propone una nueva, ni se modifica la existente.

- 8. La nomenclatura ya definida en la literatura para los sistemas de tiempo real se mantiene a menos que explícitamente se mencione en la tesis.

# 1.11 Contribuciones de este trabajo.

Se presentan las siguientes contribuciones para este trabajo de tesis:

- a) Se diseña un modelo simple dirigido para el manejo de la potencia. Específicamente, son desarrollados dos algoritmos originales eficientes para el manejo de la frecuencia y/o voltaje, considerando que el sistema tiene restricciones de precedencia y potencia, es decir que pueden ser utilizados para cualquier sistema de tiempo real que tienen como limitante el suministro de la energía y sea ejecutado en una Laptop.

- b) Los efectos producidos por otros efectos prácticos tales como niveles de frecuencia discretos y contención de acceso a memoria compartida son también tratados.

- c) Se presenta el método implementado en un algoritmo, que brinda mejor desempeño que lo referenciado en la actualidad para sistemas con un

procesador, así como también puede ser extendido para múltiples procesadores.

## **RESUMEN**

En este capítulo se describieron los conceptos básicos de los sistemas de tiempo real, describiendo el factor de utilización, así como se da la referencia para consultar las tres restricciones más importantes de un sistema de tiempo real y las definiciones de proceso. En seguida se mencionan los algoritmos de planificación para monoprocesadores y se da la referencia para consultar los algoritmos de planificación para multiprocesadores, luego el modelo del sistema que se utiliza en los próximos capítulos. También se planteó el problema a solucionar así como los objetivos de este trabajo de tesis. Posteriormente se presentó la justificación para realizar este trabajo y por último las limitaciones y alcances y las contribuciones que se obtienen al concluir esta tesis.

#### **CAPITULO 2**

#### **ESTADO DEL ARTE**

En este capítulo se muestra el estado del arte en el área de planificación de tareas de tiempo real con restricciones de precedencia y/o restricciones de potencia. Se empieza con una breve semblanza referente al ahorro de energía, presentando el consumo de potencia en los dispositivos que integran una PC portátil. Luego se detalla la tecnología de las baterías y su tecnología futura. La arquitectura para el ahorro de energía se presenta a continuación, así como la implementación para el ahorro de energía en un procesador Core 2 Duo. En seguida el consumo de energía en cuatro sistemas operativos comerciales y se continua con las técnicas y el manejo para ahorrar energía. Por último se explica brevemente los parámetros utilizados para la implementación de un procesador de velocidad variable.

Con lo anterior se propone un algoritmo que permita el planificar tareas de tiempo real con restricciones de precedencia y restricciones de potencia, tal que sea maximizado el ahorro del sistema, sin que las tareas pierdan sus plazos de respuesta. Para realizar esto se proponen dos diferentes condiciones de ejecución y una aplicación práctica, mismas que están definidas en el inciso 1.8.2 del capítulo1 y serán desarrolladas en capítulos subsecuentes.

## 2.1 Motivación.

Existen sistemas computacionales fuertemente relacionados con el entorno que les rodea y con el cual se encuentra en constante interacción. Ejemplos de este tipo de sistemas son los sistemas de adquisición de datos y los controladores industriales, los cuales están compuestos por diversos elementos (actuadores, sensores, unidades de cómputo, redes de interconexión, etc.) que deben trabajar

de forma conjunta y coordinada. Debido a la naturaleza cambiante del entorno con el que interactúan, junto con la necesidad de coordinación entre sus componentes, los resultados obtenidos sólo podrán ser considerados válidos cuando, además de ser correctos desde el punto de vista lógico, hayan sido generados a tiempo. Resultará, por tanto, preciso imponer restricciones temporales cuyo cumplimiento garantice el correcto funcionamiento del sistema. Este tipo de sistemas, capaces de realizar tareas y responder a eventos asíncronos externos dentro de unos plazos temporales determinados son los denominados "Sistemas de Tiempo Real" [61].

Para que sea posible la predecibilidad temporal del sistema completo, todas las partes que le componen deberán de presentar un comportamiento predecible. En consecuencia, en el caso de utilizar un sistema operativo, los servicios que éste proporcione a las aplicaciones deberán presentar tiempos de respuesta acotados, de forma que así sea capaz de garantizar los requerimientos temporales de los procesos bajo su control. Mientras que en un sistema operativo de tiempo compartido, como Unix [7][38], lo importante es proporcionar a los usuarios unos buenos tiempos de respuesta promedios [32], la clave en los sistemas operativos de tiempo real será garantizar los requerimientos temporales; el tiempo de respuesta promedio pasa así a un segundo plano.

Dentro de los sistemas de tiempo real, un tipo particular son los "sistemas empotrados". En este tipo de sistemas, el computador constituye una parte más de un sistema mayor en el que se encuentra altamente integrado y en el que se dedica a realizar una función (o un pequeño conjunto de ellas). Las aplicaciones tradicionales de este tipo de sistemas incluirían sistemas de control en aviones, trenes, nudos de telecomunicaciones, motores de automóviles, procesos industriales, teléfonos móviles, etc.

Recientemente el consumo de energía en computadoras ha llegado a ser muy popular no sólo para sistemas de computadoras móviles para alargar la vida de las baterías, sino también en grandes sistemas consistentes de múltiples unidades de

procesamiento para reducir el consumo de energía y el costo de enfriamiento asociado. Desde que los procesadores consumen un gran porcentaje de energía en los sistemas de cómputo, especialmente en sistemas empotrados, muchos trabajos han sido realizados para manejar el consumo de energía de los procesadores.

La capacidad y el tiempo de vida de las baterías para las computadoras portátiles han mejorado mucho en los últimos años. Sin embargo los procesadores modernos consumen mucha más energía que los anteriores y cada nueva generación de computadoras portátiles trae consigo más dispositivos que consumen más energía. Por esta razón el manejo de la energía es más importante que nunca. La necesidad de uso más prolongado de la computadora trae como consecuencia el tener uno o más reemplazos de baterías. Pudiendo lograr mucho si se utilizan políticas inteligentes para el manejo de la energía.

# 2.2 Consumo de potencia en dispositivos.

Los dispositivos que consumen más energía en una computadora portátil son: el procesador, el disco duro y la pantalla. Estos se pueden configurar por separado. El manejo de potencia del procesador permite ajustar la frecuencia del procesador para ahorrar el máximo de energía sin que se pierda el desempeño de la computadora. El manejo de potencia del disco duro permite que se coloque en el umbral de su voltaje de alimentación cuando no se está utilizando y este mismo método es utilizado para el manejo de la potencia de la pantalla. Otros dispositivos como tarjetas gráficas, tarjetas de red inalámbricas y tarjetas de USB permiten que se pasen al estado de dormido.

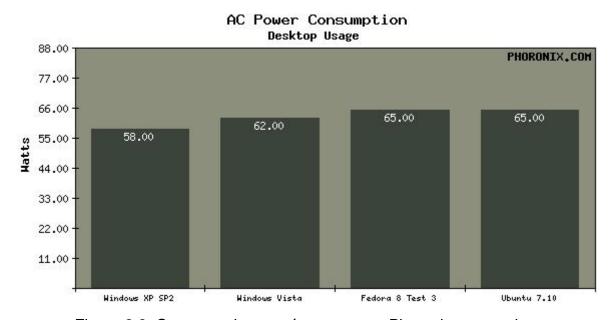

En la figura 2.1 se puede ver la distribución del consumo de potencia en los diferentes dispositivos que integran una computadora portátil.

Figura 2.1. Consumo de potencia en los dispositivos.

# 2.3 Tecnología de baterías.

Las baterías están en todas partes, desde juguetes hasta automóviles. Las más utilizadas se desechan porque no se pueden recargar; las cuales son llamadas baterías "primarias", convencionales o alcalinas y se usan en múltiples aplicaciones, algunas tan vitales como la alimentación de marcapasos. Las baterías "secundarias" o recargables satisfacen necesidades muy distintas.

Actualmente existen dos tipos de baterías recargables que dominan el mercado: las baterías de plomo y las de níquel-cadmio.

Las baterías de plomo se encuentran en los automóviles sólo destinadas para el arranque, iluminación e ignición (no tienen suficiente energía para mover el

coche). Las baterías de níquel-cadmio a falta de mejores baterías, se emplean en artículos de electrónica de consumo como videocámaras y computadoras portátiles o teléfonos móviles.

Cualquiera que sea su uso, se requiere que sea mejorada la técnica de estas baterías, ya que se descargan solas, demasiado rápidamente y presentan un peculiar efecto memoria que reduce su capacidad.

Además de la necesidad de mejorar las técnicas de las baterías actuales, se debe saber que los elementos que las componen son altamente contaminantes, especialmente el plomo y el cadmio, y que en el caso de este último, los procesos de reciclado no están bien establecidos. Sin embargo, la demanda del mercado de las baterías recargables es previsible que siga creciendo tanto a corto como a medio plazo. Así, la búsqueda de baterías más ligeras y de mayor densidad de energía para el mercado de la electrónica de consumo es ya una necesidad urgente.

A este enorme mercado mundial habría que añadir a más largo plazo el no menos importante mercado de baterías recargables para tracción de automóviles eléctricos. En este campo la necesidad de mejora es igualmente patente. De hecho las baterías son el punto débil de los prototipos eléctricos que están empezando a salir ya al mercado del automóvil. Sus prestaciones limitadas y alto precio relativo hacen dura la competencia con vehículos convencionales de combustión. Sin embargo, existe una creciente demanda social de tecnologías limpias, más respetuosas con el medio ambiente que hacen especialmente deseable el desarrollo de vehículos eléctricos al menos para uso en entornos urbanos.

En general, cada tecnología tiene características que se ajustan mejor a ciertas aplicaciones, y existen asimismo numerosos y variados tipos de baterías que se pueden considerar hoy en día en estado de desarrollo.

Una breve lista podría incluir baterías Sodio/azufre, zinc/aire, hidruro metálico/óxido de níquel y baterías de litio. Todas tienen ventajas e inconvenientes que se intentan evitar con diseños adecuados pero las *baterías de litio*, junto quizá a las de hidruro metálico son las que van encontrando un mayor consenso en cuanto a su potencial y un mayor esfuerzo en su investigación y desarrollo a nivel mundial.

Son muchas las razones que han originado este consenso. En primer lugar *el litio es el metal más ligero* y esto da lugar a una alta capacidad específica (figura 2.2), lo que permite obtener la misma energía con un peso muy inferior (figura 2.3).

Figura 2.2. Capacidad específica.

Figura 2.3. Masa necesaria...

Por otro lado, cuando un ánodo de litio metálico se combina con cátodos de ciertos óxidos de metales de transición las celdas electroquímicas reversibles que resultan presentan valores de voltaje superiores al de otros sistemas; ello contribuye a una alta densidad de energía. Además de sus características técnicas, la tecnología de litio es de las más versátiles y puede llegar a encontrar aplicaciones comerciales en muy distintos ámbitos, desde los que requieren pequeñas y delgadas micro baterías hasta baterías de alta capacidad y reducido peso para automóviles. Finalmente, y a diferencia del plomo o cadmio, los materiales que componen las baterías de litio más prometedoras no representan un problema de posible contaminación ambiental.

En los primeros prototipos de baterías de litio, el electrodo positivo (cátodo) era normalmente un óxido o sulfuro metálico con la capacidad de intercalar y desintercalar iones litio en los procesos de descarga y carga de la batería de un modo reversible; el electrodo negativo (ánodo) en estos primeros sistemas estaba constituido por litio metálico que debía sufrir procesos igualmente reversibles de disolución durante la descarga y deposición durante la recarga. Para llegar a ser

realmente aplicables las baterías de litio han tenido que superar inconvenientes, algunos de ellos graves. El más serio obstáculo para la comercialización de baterías de litio recargables se derivó precisamente de la gran reactividad del litio metálico que podría representar problemas de seguridad; el uso del metal como ánodo se vio asociado a problemas de crecimiento dendrítico del litio durante los procesos de recarga continuados.

Este comportamiento llegó a ser causa de problemas de funcionamiento y seguridad. Afortunadamente estos problemas se resolvieron de forma totalmente satisfactoria con la introducción de dos variantes dentro de esta tecnología: las baterías de "ion-litio", y el desarrollo de electrolitos poliméricos plásticos menos reactivos que sus análogos líquidos. En las baterías de ion-litio el ánodo no está formado por litio metálico sino por otro material mucho más seguro, como por ejemplo el grafito, capaz de intercalar (o almacenar) iones de litio en una forma menos reactiva que la del litio metálico, sin un notable detrimento de su densidad energética.

Durante la descarga: Los iones litio cambian espontáneamente del electrodo negativo al electrolito y de éste al electrodo positivo. El electrolito permite el paso de iones pero no de electrones. Al mismo tiempo, los electrones fluyen espontáneamente del electrodo negativo al positivo a través del único camino que les dejamos libre: a través del circuito eléctrico. A medida que avanza la descarga, el potencial de cada electrodo cambia de forma que su diferencia disminuye y cae por tanto el voltaje de la celda a medida que sacamos carga eléctrica (Q) de la batería.

Durante la carga: Se bombea electrones en el electrodo negativo y son extraídos del positivo. Haciendo por tanto el electrodo negativo más negativo y el positivo más positivo y se aumenta, así la diferencia de potencial entre ellos, o lo que es lo mismo, el voltaje de la celda. Este proceso fuerza también a los iones litio a salir del electrodo positivo y a intercalarse en el negativo.

Este gran avance no sólo representó la introducción de una tecnología mucho más segura, sino que introdujo ventajas adicionales como el excelente comportamiento de reversibilidad durante los procesos de carga y descarga que es característico actualmente de las baterías de ion-litio.

Las baterías recargables de ión-litio que están en el mercado están compuestas de cátodos de LiCoO2, electrolitos poliméricos y ánodos de grafito altamente densificados y con poca superficie para minimizar los fenómenos de pasivación que también les afectan. Se pueden recargar hasta 2500 veces y gracias a su bajo precio constituyen la mejor alternativa en el mercado de la electrónica de consumo.

# 2.3.1 Tecnología futura.

Puede una computadora portátil funcionar durante 10 horas o más antes de recargarse. Eso es lo que promete una nueva tecnología de baterías llamada células directas de combustible metanol (DMFC, por sus siglas en inglés). La DMFC, una posible sucesora de las baterías recargables y desechables que utilizan muchos de los dispositivos digitales móviles de hoy, genera energía mezclando el metanol con aire y agua.

El problema es que casi todas las compañías todavía están buscando la manera de aumentar la potencia que producen las DMFCs. Dentro de la célula de combustible, el agua y el metanol deben estar separados del catalizador por medio de una membrana. Mientras mayor sea la relación de metanol a agua, más potente será la DMFC (y más pequeña pudiera ser). Tampoco se ha decidido si las nuevas DMFCs serán desechables o recargables. Samsung recientemente mostró un prototipo de DMFC para portátiles. NEC también está trabajando en un modelo para PCs portátiles, e Hitachi tiene planes de vender una para PDAs.

# 2.4 Arquitectura para el ahorro de energía.

Minimizar el consumo de energía es uno de los principales objetivos de muchos usuarios de computadoras. Para los usuarios de laptop, ésto se refleja en la vida útil de la batería. Para los usuarios de una PC de escritorio, ésto afecta las necesidades de enfriamiento y, por tanto podrá causar problemas con el ruido de los ventiladores dentro de una oficina.

Para los usuarios de servidores, el costo de energía y de enfriamiento es una parte creciente de los gastos operacionales de un centro de datos. Para ayudar a enfrentar estos desafíos, los investigadores de Intel desarrollaron una nueva arquitectura de sistema para consumo y ahorro de energía (EESA) creada para aumentar el desempeño por watt por medio de la gestión del voltaje y de la frecuencia. La EESA utiliza sensores para identificar cuándo una función del sistema está ociosa y después envía este componente a un estado más bajo de consumo de energía. Los desarrolladores de la EESA utilizaron el trabajo conjunto de cinco tecnologías para minimizar el consumo y maximizar el ahorro de energía. Estas tecnologías son:

- Gestión de energía refinada

- Optimización de E/S

- Conversión de energía del sistema

- Arquitectura con sensor para cliente

- Gestión de la política de energía

Gestión de energía refinada (FGPM). La función de gestión de energía refinada (FGPM) es importante para la EESA y ofrece un control más preciso sobre los índices de energía dentro del sistema. Actualmente, la función de espera (sleep) del sistema se inicia sólo cuando todos los componentes están ociosos. La función FGPM, colocará funciones individuales del sistema en el estado de espera cuando

éstas estén ociosas, lo que dará como resultado un menor consumo de energía y un mayor ahorro de energía.

Optimización de E/S. La tecnología de la Optimización de E/S es capaz de reducir el consumo de energía en tres áreas utilizadas por el usuario: displays con pantallas con actualización automática, E/S administradas por la energía y audio con pantallas con actualización automática. La tecnología de la Optimización de E/S observa las interfaces de estos dispositivos para encontrar las maneras de reducir sus dependencias entre los ciclos de procesamiento del sistema. Si las funciones del sistema pudieran colocarse en el estado ocioso más frecuentemente, consecuentemente el consumo de energía será reducido. Los displays con pantallas con actualización automática se benefician por el hecho de que el contenido de la mayoría de los displays de computadoras no cambia muy rápidamente si estuvieran asociados a una PC de escritorio, una laptop, una PDA, o un teléfono celular. Esta es la naturaleza de las interacciones humanas con computadoras que llevan a los usuarios en poco tiempo a asimilar las informaciones que están exhibiéndose; por tanto los displays pueden permanecer inalterados algunos segundos hasta varios minutos por vez. En cuanto a eso, la lógica de gráficos por detrás del display consume energía al restaurar la pantalla varias veces por segundo. Los investigadores de Intel inventaron la función del display con pantallas con actualización automática para permitir que la lógica del display se coloque en espera cuando la pantalla está actualizándose. La idea es instalar una pequeña cantidad de memoria—la cual es cada vez más barata—en el propio panel del display. Esta memoria del caché almacena las informaciones que serán exhibidas al usuario. Durante el tiempo que el display no esté siendo alterado, éste toma la información del caché, como consecuencia la energía se reducirá colocando la lógica restante del display en espera.

En el futuro, la tecnología de display con pantallas con actualización automática será incorporada en los dispositivos móviles. Cuando una red sin cable sondea el dispositivo, un dispositivo de la EESA responderá a partir de un caché con

pantallas con actualización automática en vez de activar todo el procesador y el chipset para responder al sondeo. La tecnología de la E/S administradas por la energía ofrece realimentación a la función FGPM sobre el estado de la gestión de energía de los dispositivos del puerto USB (Universal Serial Bus) integrados en la computadora (dispositivos de E/S externos no son afectados). Si el dispositivo de USB estuviera ocioso, la FGPM lo coloca y el chipset lo direcciona hacia el modo en espera hasta que sus servicios sean necesarios. La función de audio con pantallas con actualización automática mantiene un gran buffer de audio que es usado para llevar la salida de audio al usuario. Después, el controlador de disco del sistema es accesado sólo ocasionalmente cuando el buffer necesite restaurarse. En el transcurso de estos accesos, el disco, el procesador y otros circuitos no utilizados pueden colocarse en estado de baja potencia o en estado de conservación de energía. El usuario continúa escuchando ininterrumpidamente, pero el resto de la máquina permanece desconectado el tiempo suficiente para reducir el consumo de energía.

Conversión de la energía del sistema. La función de conversión de la energía del sistema organiza el modo en como la energía es administrada desde su fuente hasta los circuitos que la utilizan. Las repetidas conversiones de energía, en las actuales computadoras, resultan en economías menores que un 50%— esto significa que la mitad de la energía es consumida en los propios procesos de conversión. Los investigadores de Intel están desarrollando métodos para mejorar estas economías, con el objetivo de alcanzar un 90% de reducción. Además, la función de conversión de la energía del sistema reaccionaría a temperaturas más altas del sistema por medio de la disminución de la velocidad del reloj en algunos componentes con el fin de disminuir el consumo y aumentar el ahorro de energía durante el proceso de conversión de energía. Disminuir el reloj significa reducir el consumo de energía en los circuitos CMOS, bajar la temperatura y permitir una mayor economía en el convertidor de energía. Para servidores con láminas (ver apéndice C), los sensores podrán ofrecer información a la FGPM para ayudar a balancear las cargas de la computadora utilizando una pila de láminas, de este

modo, se reduce la salida térmica de cada pila como un todo. Por ejemplo, si una lámina estuviera trabajando bastante y estuviera generando bastante calor, una segunda lámina subutilizada podría realizar parte del trabajo de la primera lámina, así el calor total generado por ambas láminas es reducido. Además, la función de conversión de la energía del sistema permitirá que componentes ociosos de un servidor de láminas se desconecten para conservar la energía y reducir la generación de calor. La necesidad de reducir la energía mediante el enfriamiento podría reducir aún más el consumo de energía cuando algunos ventiladores este desconectados. Estos mismos principios de la conversión de la energía del sistema también pueden beneficiar los dispositivos portátiles. La tecnología de Conversión de energía del sistema puede convertir la energía de la batería de forma más eficiente—permitiendo más horas de uso a los usuarios de los dispositivos móviles.

Arquitectura con sensor para cliente La arquitectura con sensor para cliente estandariza el modo como los sensores se comunican con la FGPM. Actualmente no existe ningún mecanismo para que varios sensores pasen su información de vuelta para la función de administración central. La arquitectura con sensor para cliente fue creada para organizar los sensores por medio de la identificación de sus capacidades, del monitoreo de sus funciones y de la definición de un proceso metódico para obtener informaciones para la FGPM de manera sistemática.

**Gestión de la política de energía** La tecnología de la gestión de la política de energía incorpora todas las informaciones anteriores y las controla, para maximizar totalmente la economía de la energía para la plataforma.

### 2.5 Manejo de potencia en el procesador Core 2 Duo.

Cuando AMD sacó al mercado sus procesadores Dual-Core no quedaron dudas: la arquitectura NetBurst se encontraba en sus límites, así como, basado en un

diseño que hizo popular a Intel en su época, nace el **Conroe**, un procesador que viene a reivindicar a Intel y que trae aparejado todo el beneficio del conocimiento que la empresa vino aprendiendo en todos estos años.

# 2.5.1 Análisis de la arquitectura:

Enfrentados a todos los problemas y limitaciones que la arquitectura NetBurst les dio en los últimos dos años, los ingenieros de Intel se propusieron dos metas fundamentales en esta nueva arquitectura: una es una mayor efectividad por reloj que la arquitectura anterior y la otra es un menor consumo de energía. Son 2 metas que curiosamente van en contra de lo que Intel nos estuvo mostrando en sus últimos procesadores Presler, por ejemplo. Aquí es donde vemos cómo las falencias o error involuntario en la arquitectura NetBurst no fueron tomadas como una derrota por parte de Intel sino como una forma de poder mejorarse y es justamente por eso que las metas que se impusieron esta vez fueron bien claras y muy exigentes.

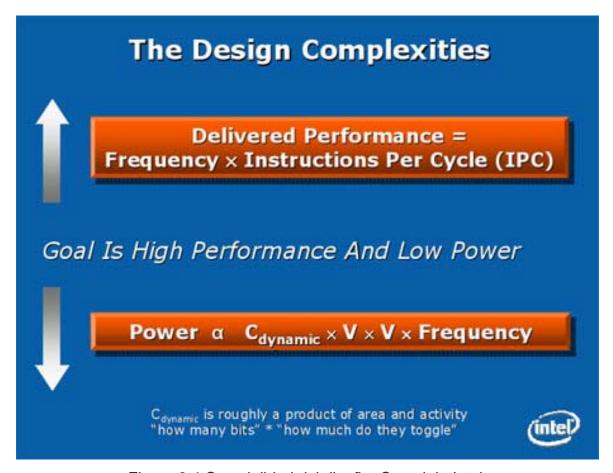

Figura 2.4 Complejidad del diseño. Copyright Intel.

En cualquier diseño de procesadores, hay ciertas variables matemáticas que se deben respetar, ya que son éstas las bases para lograr una arquitectura eficiente. Estas son, "C dynamic", Voltaje y Frecuencia (ver figura 2.4). Estas 3 variables dictan el consumo, frecuencia y movimiento de bits a lo largo de una arquitectura determinada. Debido a que estas variables se encuentran conectadas entre sí, cualquier modificación a una, afecta a la otra.

Lo primero que vemos es que la relación Voltaje x Frecuencia es 2 veces mayor. Esto quiere decir que por cada vez que el procesador sube linealmente su frecuencia de operación, aumenta de forma cuádruple su consumo de energía, esto es perfectamente válido en Overclocking, ya que aplicamos el concepto

opuesto para la misma ecuación, cuando un procesador llega a su límite de clock, es necesario subir el voltaje para permitirle obtener un clock más alto. Pero, como bien vemos en la ecuación, es necesario cuadruplicar el voltaje necesario para apenas subir linealmente su frecuencia. Al ver estos valores, se hizo claro para Intel que elevar su frecuencia de operación no es una opción, como tampoco jugar con el voltaje. La otra forma de elevar el rendimiento de un procesador es claro que está aumentando la cantidad de unidades de ejecución que conlleva en general a aumentar la eficiencia, esto es, la cantidad de instrucciones por ciclo de reloj que un procesador puede realizar, pero es aquí donde aparece la siguiente limitación.

El valor que todavía no mencionamos qué es el "C dynamic", explicar el funcionamiento de esta variable digamos que no es muy fácil, y es por eso que se decide expresarlo en castellano, para que pueda ser entendido. C dynamic es el valor que expresa el producto de un área de actividad de bits, o lo que es lo mismo que decir "cuantos bits" existen en un momento dado en nuestra área determinada, para este caso, el procesador. La cantidad de bits que en un momento determinado se mueven en el procesador determina el área total del "C dynamic". Como pueden ver, es un área no definida por un espacio físico ni por silicio, sinó más bien por "bits activos" en la arquitectura. El problema con esta variable es que a mayor número de bits activos existe, claro está, mayor energía, y por lo tanto, se eleva nuevamente el voltaje del procesador, negando toda posibilidad de lograr una arquitectura con bajo consumo.

Para elevar efectivamente el rendimiento, se deben aumentar la cantidad de unidades de ejecución, esto conlleva a una mayor cantidad de transistores y por consiguiente, potencialmente mayor cantidad de bits activos en un momento dado en el procesador. Esto directamente nos lleva a un aumento en el nivel de energía que el procesador consume y por tanto, aparece nuestro dilema.

El problema se evidencia en procesadores como el Presler, donde una excesiva

cantidad de transistores y su largo Pipeline de Ejecución provocan una gran cantidad de "bits activos" combinado esto con la baja eficiencia de instrucciones por segundo y con un alto clock elevan el consumo de energía a niveles desproporcionados, es por esto que el proceso de manufactura no afecta ni contribuye automáticamente a una mejor eficiencia en el procesador ni en el consumo, ya que el área de "C dynamic" no se encuentra definida por un proceso de miniaturización.

Aquí Intel se enfrenta a su segundo dilema, ya que debe lidiar con el problema de mejorar la arquitectura por medio de una mejor unidad de ejecución sin que esto introduzca una mayor carga de "bits activos", para lo cual recurrió a una serie de "trucos" por así decirlo que aprendió a lo largo del tiempo y por sobre todo con sus últimos procesadores Pentium-M.

En base a esta descripción, se analiza puntualmente por qué esta nueva arquitectura es más eficiente y consume menos energía.

Se añadieron cinco nuevas características para darle un mejor desempeño y un ahorro de energía mayor, estas características son las siguientes:

- 1) Amplia ejecución dinámica (Wide Dynamic Execution).

- Impulsar los medios digitales avanzados (Advanced Digital Media Boost).

- 3) Capacidad de potencia inteligente (Intelligent Power Capability).

- 4) Acceso a memoria inteligente (Smart Memory Access).

De estas cuatro características sólo se explicará la capacidad de potencia inteligente.

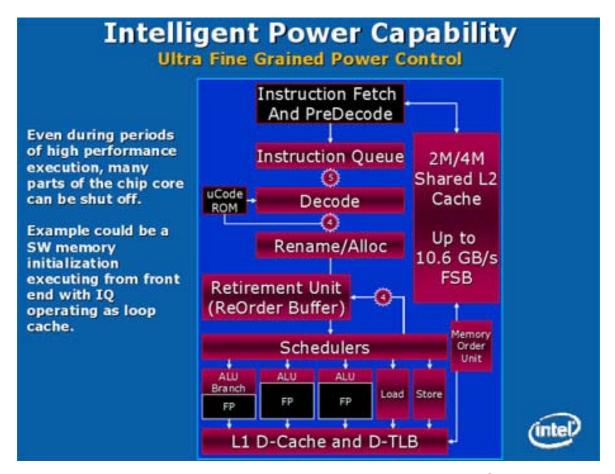

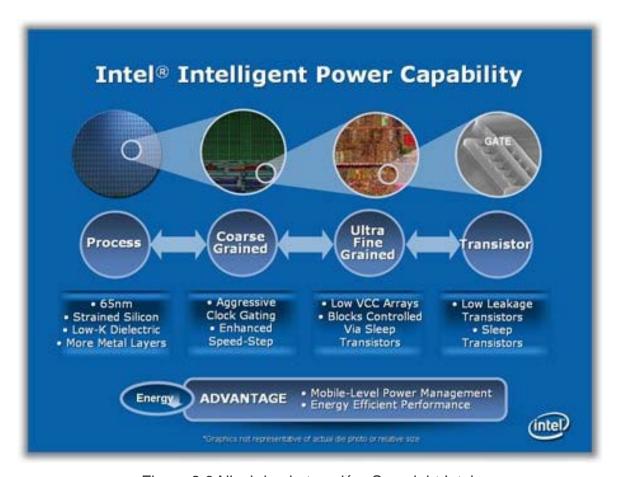

### Intel Intelligent power capability:

Debido a que el consumo de energía es el punto más importante para Intel en esta nueva arquitectura (ver figura 2.5), se tomaron pasos intensivos para llegar al nivel

incluso más pequeño en lo que respecta a control de la energía que se administra a cada parte del procesador.

Figura 2.5. Arquitectura de la capacidad de potencia inteligente. Copyright Intel.

Como dicen los Ingenieros de Intel, el acercamiento que emplearon es el mismo que el de la Ley hacia las personas, "Ninguna parte del procesador es digna de ser utilizada hasta que demuestre lo contrario", y así es, la arquitectura Core utiliza un nivel muy refinado de desactivación a nivel "gating" que le permite desactivar prácticamente enormes cantidades del procesador cuando no se usan y deberán realmente demostrar una necesidad de utilización para re-activarse, esto salva una enorme cantidad de energía que no se utilizará, bajando el consumo y la generación de calor.

Figura 2.6 Nivel de abstracción. Copyright Intel.

Existen varios modos de dormir incluso hasta el modo que intel denomina sueño profundo (Deep Sleep), lo interesante de esta tecnología es la parte de "Intelligent", como su nombre lo indica; existen momentos donde en general, el procesador no se encuentra haciendo demasiadas cosas, imaginen un escenario, donde un procesador Dual Core, se encuentran en la pantalla inicial de Windows con tan sólo un programa de Mensajería y un navegador abierto, en este tipo de casos e incluso cuando nos encontramos jugando con algún juego que no utiliza Multithreading, es común que uno de los Cores (e incluso gran parte de tiempo del otro) no se utilicen, en este caso, la tecnología de ahorro de energía es capaz de desactivar enormes porciones de sistemas del procesador en desuso, incluso al nivel de dejarlo casi en stand-by, lo interesante es que no sólo se realiza mediante

Speed-steep (reducción del multiplicador) sino que se realiza a nivel muy interno (ver figura 2.6) a nivel transistores, lo cual le permite tener un control casi absoluto de qué es lo que hace cada parte de la arquitectura y qué partes pueden desactivarse, esta tecnología se encuentra "finamente" perfeccionada desde el Pentium-M, recuerden que su antecesor fue un procesador para computadoras portátiles donde el ahorro de energía es absolutamente importante.

La serie de adiciones que hizo Intel en esta nueva arquitectura realmente merecen mencionarlas como "Revolucionarias" por varios factores: primero, lograron duplicar e incluso triplicar el rendimiento de su antecesor, el Pentium4, claro está con otra arquitectura, pero con igual o mayor mérito, ya que pudieron aprender de sus propios errores y lo más importante es que lo hicieron a expensas de bajar considerablemente el consumo de energía, cosa difícil de hacer, muy difícil, pero que han demostrado ser posible, jugando con variables y aplicando todos los trucos aprendidos en el Pentium-M. Todo esto tuvo sus frutos en un Procesador que es increíblemente eficiente, sumamente fresco en operación y que tiene amplias posibilidades y un gran futuro por delante.

# 2.5.2 Administración de energía:

#### APM –ACPI

Todas las técnicas de gestión de energía (power management) requieren un hardware y una rutina de la BIOS apropiados. La mayoría de los ordenadores portátiles y muchos ordenadores de sobremesa y servidores cumplen estos requisitos.

En el hardware más antiguo se utiliza con frecuencia el estándar APM (Advanced Power Management). Debido a que APM consiste básicamente en un conjunto de funciones implementadas en la BIOS, existen diferencias en el soporte de APM en las distintas clases de hardware.

ACPI es todavía más complejo y la calidad de su soporte depende incluso en mayor medida del hardware utilizado.

# Funciones para el ahorro de energía:

# Stand-by (en reposo)

Solo se desactiva la pantalla y en algunos dispositivos se reduce también el rendimiento del procesador. No todas las implementaciones APM ofrecen esta función. En ACPI este estado se corresponde con S1.

# Suspend (to memory)

Para este modo toda la información sobre el estado del sistema se guarda en la memoria y aparte de esta, todo el resto del sistema se detiene. Es un estado en el cual la computadora gasta muy poca energía. El atractivo especial de realizar esto con Linux es el no tener que parar el ordenador nunca; hay otros sistemas operativos que se vuelven inestables después de cierto tiempo. En la mayoría de los portátiles actuales basta con cerrar la tapa para suspender y abrirla después para seguir trabajando. En ACPI este estado se corresponde con S3. El soporte de este estado depende enormemente del hardware utilizado.

## **Hibernation (suspend to disk)**

En este modo, la computadora vuelca todo el contenido de la memoria al disco duro y el sistema se detiene después. El ordenador tarda de 30 a 90 segundos de salir de este período de hibernación. Tras este periodo se restablece por completo el estado anterior al suspend. Algunos fabricantes ofrecen ciertos modos híbridos (por ejemplo RediSafe en IBM Thinkpads). En ACPI el estado de hibernación se corresponde con S4.

#### Control de batería

Junto a la información del estado de la batería también es importante tener algo previsto en caso de que disminuyan las reservas de energía. ACPI o APM desempeñan aquí esta función de control.

### Apagado automático

Después de un shutdown la computadora se para completamente sin necesidad de pulsar el botón de apagar. Esto es importante en caso de que se realice un apagado automático poco antes de que se agote la batería.

## Apagado de los componentes del sistema

El componente esencial a la hora de ahorrar energía es el disco duro. Dependiendo de la fiabilidad del sistema, éste se puede poner a dormir durante más o menos tiempo. El riesgo de una perdida de datos se incrementa con la duración del período de reposo de los discos. Se puede desactivar otros componentes vía ACPI (al menos en teoría) o de forma duradera en el setup de la BIOS.

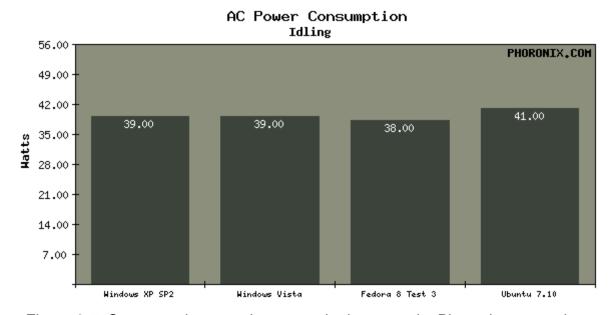

### Control del rendimiento del procesador