### INSTITUTO POLITECNICO NACIONAL

## CENTRO DE INVESTIGACIÓN EN COMPUTACIÓN

# DISEÑO DE UN CIRCUITO PARA LA EVALUACIÓN DE LA TRANSFORMADA RÁPIDA DE FOURIER UTILIZANDO LÓGICA PROGRAMABLE

#### **TESIS**

# QUE PARA OBTENER EL GRADO DE MAESTRO EN CIENCIAS EN INGENIERIA DE CÓMPUTO CON OPCIÓN EN SISTEMAS DIGITALES

# PRESENTA NAYELI VEGA GARCÍA

DIRECTORES DE TESIS

M. en C. OSVALDO ESPINOSA SOSA

M. en C. VICTOR HUGO GARCÍA ORTEGA

SIP-14 bis

# INSTITUTO POLITÉCNICO NACIONAL

# SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

# ACTA DE REVISIÓN DE TESIS

| En la Ciudad d  | de            | México, D.F.                       | siendo las                  | 16:00          | horas    | del día             | 3          | del mes de  |

|-----------------|---------------|------------------------------------|-----------------------------|----------------|----------|---------------------|------------|-------------|

| junio d         | e 2013 s      | se reunieron los                   | miembros de la              | Comisión F     | Revisora | de la Te            | sis, desig | gnada       |

| por el Colegio  | de Profeso    | res de Estudios                    | de Posgrado e               | Investigació   | n del:   |                     |            |             |

|                 |               | Centro d                           | e Investigació              | in en Comp     | utación  |                     |            |             |

| para examinar   | la tesis titu | lada:                              |                             |                |          |                     |            |             |

| "Diseño         | de un circ    | uito para la evalu                 | ación de la Tra<br>programa |                | ápida de | Fourier             | utilizando | o lógica    |

|                 |               |                                    |                             |                |          |                     |            |             |

| Presentada por  | el alumno:    |                                    |                             |                |          |                     |            |             |

|                 | GA            |                                    | GARCÍA                      |                |          |                     | AYELI      |             |

| Apen            | do paterno    |                                    | Apellido materno            | on registro:   | Δ        | 1 1                 | Nombre(s)  | 8 7         |

| annienata das B | MAEOTDÍA I    | EN CIENCIAO EN                     |                             | -              |          | OLÓN EN             |            |             |

| aspirante de: I | MAESTRIA      | EN CIENCIAS EN                     | INGENIERIA D                | E COMPUTO      | CON OF   | CION EN             | SISTEM     | AS DIGITALE |

|                 |               | iar opiniones l<br>ue satisface lo |                             |                |          |                     |            |             |

|                 |               | LA                                 | COMISIÓN R                  | EVISORA        |          |                     |            |             |

|                 |               | _                                  | Directores de               | Tesis          | W        | /                   |            |             |

|                 | . (           | (C-                                |                             |                | N.M      | ,                   |            |             |

|                 | St            | LQ A                               |                             |                | {X//     | 1)                  |            |             |

|                 | - 1           | July 1                             |                             |                | X\V/     | /                   |            |             |

| M. e            | n C. Osvald   | Espinosa Sosa                      |                             | M. en C        | . Victor | lugo Garo           | ia Ortega  | i i         |

|                 |               | 1                                  |                             |                |          |                     |            |             |

|                 |               | 01                                 | _                           |                | ~        |                     |            |             |

|                 |               |                                    |                             |                | 1/2 an   | mif                 |            |             |

|                 |               | 2/                                 |                             | Dr. Mar        | /        | io Pamier           | - Calinaa  |             |

|                 | Dr. Sergio Si | uárez-Guerra                       |                             | Dr. Mar        | co Anton | io Ramire           | z Salmas   | )           |

|                 | //            |                                    | )                           |                |          | $\propto$           | )          |             |

|                 | //            |                                    |                             |                | _        | $\mathcal{H}_{c}$ . | /          |             |

| (               | 1 7           | n.                                 |                             |                | GIL.     | 1.610               |            |             |

| The state of    | gse Les Or    | opeza Rodriguez                    |                             | M. en C        | . Romeo  | Urbieta P           | arrazales  | 3.          |

|                 | /             |                                    |                             | December 25    |          |                     |            |             |

| /               |               |                                    | Á                           |                |          |                     |            |             |

| /               |               | PRESIDENTE DI                      | EL COLEGIO                  | E PROFES       | ORES     |                     |            |             |

|                 | -             | RESIDENTE DI                       | A COLLOID I                 | ) KOPES        | ONEO     |                     |            |             |

|                 |               |                                    | FA W/W                      | 10.357968 N    | 100004   |                     |            |             |

|                 | _             |                                    | Amis Alfohao V              | la Vargas      | TON!     | -                   |            |             |

|                 |               | - 1                                | 7                           | EN CONPUTATION |          |                     |            |             |

|                 |               |                                    | / ib                        | RECOM          | DIE      |                     |            |             |

# INSTITUTO POLITÉCNICO NACIONAL SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

# CARTA CESIÓN DE DERECHOS

En la Ciudad de México, D. F. el día 12 del mes de Junio del año 2013, el (la) que suscribe Naveli Vega García alumna del Programa de Maestría en Ciencias en Ingeniería de Cómputo con opción en Sistemas Digitales con número de registro A110873 adscrita al Centro de Investigación en Computación, manifiesta que es autor (a) intelectual del presente trabajo de Tesis bajo la dirección de M. en C. Osvaldo Espinosa Sosa y M. en C. Victor Hugo García Ortega y cede los derechos del trabajo intitulado "Diseño de un circuito para la evaluación de la Transformada Rápida de Fourier utilizando lógica programable", al Instituto Politécnico Nacional para su difusión, con fines académicos y de investigación.

Los usuarios de la información no deben reproducir el contenido textual, gráficas o datos del trabajo sin el permiso epreso del autor y/o director del trabajo. Este puede ser obtenido escribiendo a la siguiente dirección nvegag0126@gmail.com. Si el permiso se otorga, el usuario deberá dar el agradecimiento correspondiente y citar la fuente del mismo.

Nombre y firma

Agradecimientos

# Agradecimientos

Al Consejo Nacional de Ciencia y Tecnología, CONACYT, por su apoyo durante mis estudios de maestría.

#### A mi alma mater:

El Instituto Politécnico Nacional y al Centro de Investigación en Computación por darme la oportunidad de ser parte de una comunidad en donde comencé mi formación como profesionista desarrollando mis estudios de maestría.

A mis asesores de tesis M. en C. Osvaldo Espinosa Sosa y M. en C. Victor Hugo García Ortega por sus acertadas sugerencias, consejos, tiempo y su invaluable ayuda durante el desarrollo de esta tesis y no con menos importancia a todos los profesores investigadores con los que tuve la oportunidad de trabajar por las enseñanzas impartidas.

Dedicatorias

# **Dedicatorias**

A mis padres Jaime Vega Pérez y Blanca García ...

Con profundo respeto por el gran ejemplo de vida que dan.

A mis hermanos Sarai, Jaime y Paulina ...

Por todas las experiencias que hemos vivido, esperando dar un buen ejemplo y porque sigamos trabajando y creciendo juntos como hasta ahora.

A mis amigos...

Por el apoyo y palabras de aliento brindadas durante la realización de este trabajo. Resumen

# Resumen

La Transformada discreta de Fourier es una herramienta muy importante para el procesamiento digital de señales puesto que permite obtener el espectro de frecuencias de una señal discreta en el tiempo, esto permite realizar tareas como compresión de datos, convoluciones, filtrado de señales entre otras, sin embargo, obtener el espectro de frecuencias utilizando este método requiere de una gran cantidad de recursos por lo que se utiliza el algoritmo de la transformada rápida de Fourier que permite realizar el mismo trabajo reduciendo tiempo y recursos requeridos. Contar con hardware dedicado a la evaluación de la FFT da pie a la generación de diversas aplicaciones del procesamiento digital de señales, como las ya mencionadas. Opciones para la implementación hardware de este algoritmo existen muchas, sin embargo, en años recientes el hardware reconfigurable ha mostrado tener grandes ventajas sobre otras existentes puesto que el esfuerzo de implementación es de nivel medio obteniendo buenos resultados.

Por las características del algoritmo de la FFT, la implementación hardware puede hacerse de diversas formas teniendo como ventaja el uso de hardware reconfigurable, en este trabajo se utilizó la técnica de implementación en cascada que permitió la reutilización de hardware por cada etapa del algoritmo combinado con un esquema de memoria *non-inplace* que facilitó la eliminación de dependencias de datos entre cada etapa de la arquitectura. Esta propuesta tiene la característica de ser fácilmente reconfigurable permitiendo así variar el número de puntos a evaluar haciendo pequeños cambios en las unidades de control sin modificar la ruta de datos de la arquitectura.

Finalmente se obtuvo una arquitectura que evalúa el algoritmo de la FFT para 512 puntos en un tiempo de 5.16µs a una frecuencia máxima de operación de 49.41 MHz, permitiendo un ancho de banda de 49.41 MHz con un error absoluto de 7.02 unidades en el peor de los casos, evaluando hasta 9 productos complejos por ciclo de reloj una vez que el *pipeline* se encuentra lleno. Los resultados obtenidos fueron comparados con los resultados de la evaluación realizada por Matlab y por un programa codificado en C para finalmente concluir que la arquitectura propuesta se desempeña de manera adecuada.

Abstract

# **Abstract**

The Discrete Fourier transform is a very important tool in digital signal processing since it allows to obtain the frequency spectrum of a discrete signal in time, allowing to perform tasks such as data compression, convolutions, signal filtering and many others, but the frequency spectrum obtained using this method requires a lot of computing resources, so the Fast Fourier Transform algorithm is used. The same amount of work is done with reduced time and resources. Having hardware dedicated to evaluate the Fast Fourier Transform leads to the generation of applications in digital signal processing. Options for hardware implementation of this algorithm are many and varied, as, in recent years, reconfigurable hardware has shown to have great advantages over other existing methods since the implementation effort is of medium difficulty with very good results.

Given the properties of the FFT algorithm, its hardware implementation can be done in various ways, and taking advantage of using reconfigurable hardware, the cascade implementation technique was used, that allowed the reuse of hardware for each stage of the algorithm, combined with a pattern of non-inplace memory which facilitated the removal of data dependencies between each stage of the architecture. This proposal allows the system to be readily reconfigurable, thereby enabling to vary the number of items to be evaluated by making small changes in the control units without changing the data path architecture.

An architecture was designed that evaluates FFT algorithm for 512 points in a 5.16µs time at a maximum frequency rate of 49.41 MHz, allowing bandwidth of 49.41 MHz with an absolute error of 7.02 units in the worst case, evaluating up to 9 complex products per clock cycle once the pipeline is full. The results were compared with those evaluated by programs written in Matlab and C. We conclude that the proposed architecture performs adequately.

# Glosario

- **ASIC**: Por sus siglas en inglés, *Aplicattion-specific integrated circuit*. Es un circuito integrado diseñado a la medida para realizar una función en particular. Por ejemplo, un circuito amplificador operacional es un ASIC.

- **DFT**: Por sus siglas en inglés, *Discrete Fourier transform*. Es un tipo de transformada discreta utilizada en el análisis de Fourier. Permite la obtención del espectro de frecuencias de una señal discreta en el tiempo.

- **DSP**: Por sus siglas en inglés, *Digital Signal Processor*. Es un sistema con base en un procesador o microprocesador que posee un conjunto de instrucciones, hardware y software optimizados para aplicaciones que requieran operaciones numéricas en tiempo real, específicamente para aplicaciones de procesamiento digital de señales.

- **FFT**: Por sus siglas en inglés, *Fast Fourier Transform*. Es un algoritmo que permite calcular la transformada de discreta de Fourier, propuesto por Coley y Tukey en 1965 que tiene gran importancia pues permitió el ahorro de tiempo y recursos para la obtención del espectro de frecuencias de una señal.

- **FPGA**: Por sus siglas en inglés, *Field Programable Gate Array*. Es un dispositivo lógico programable que contiene bloques de lógica cuya interconexión y funcionalidad puede ser configurada mediante un lenguaje de descripción especializado.

- **LE**: Por sus siglas en inglés, *Logic Element*. Es la unidad lógica más pequeña en la arquitectura del FPGA (Altera). Como principal característica contiene una tabla de búsqueda (LUT, *look-up table*) de cuatro entradas, que es un generador de funciones, por lo que puede implementar cualquier función de cuatro variables.

- VHDL: Por sus siglas en inglés, *Very High Speed Integrated Circuit Hardware Description Lenguage*, lenguaje creado a partir de un proyecto promovido por el gobierno de Estados Unidos en 1981 y fue homologado por el IEEE en 1987 en el estándar 1076-87. VHDL utiliza una metodología de diseño de arriba hacia abajo (*top-bottom*) que permite describir el circuito de forma estructural (señales y sus

Glosario

conexiones) y funcional (qué hace). Cada bloque se puede definir empleando sub-circuitos definidos en el mismo proyecto o disponibles en bibliotecas propias o de terceros.

**FIFO:** Tipo de memoria de rápido acceso el cual funciona bajo un esquema *first in* - *first out* (primero en entrar - primero en salir).

IPC: Número de instrucciones ejecutadas en un procesador por ciclo de reloj

CPI: Ciclos de reloj necesarios por cada instrucción ejecutada en un procesador

# Índice de contenido

| Resume   | n                                                                             | Vl       |

|----------|-------------------------------------------------------------------------------|----------|

| Abstrac  | t                                                                             | VII      |

| Glosario | 0                                                                             | VIII     |

| Índice d | le contenido                                                                  | X        |

| Índice d | le figuras                                                                    | XIII     |

| Índice d | le tablas                                                                     | XVIII    |

| Capítul  | o 1. Introducción                                                             | 1        |

| 1.1      | Antecedentes                                                                  | 1        |

| 1.2 I    | Planteamiento del problema                                                    | 5        |

| 1.3      | Objetivos                                                                     | <i>6</i> |

| 1.3.1    | Objetivo general                                                              | <i>6</i> |

| 1.3.2    | Objetivos específicos                                                         | <i>6</i> |

| 1.4 J    | Sustificación                                                                 | 7        |

| 1.5      | Alcances y límites                                                            | 8        |

| Capítul  | o 2. Marco teórico y estado del Arte                                          | 9        |

| 2.1      | Гransformada rápida de Fourier                                                | 9        |

| 2.1.1    | Algoritmo de la FFT Radix-2                                                   | 11       |

| 2.2 I    | Formato de punto fijo para la representación de números fraccionarios         | 15       |

| 2.3      | Cómputo reconfigurable para el Procesamiento Digital de Señales               | 17       |

| 2.4      | Arquitecturas para la evaluación de la FFT con base en cómputo reconfigurable | 20       |

| 2.4.1    | Procesador secuencial                                                         | 21       |

| 2.4.2    | Procesador en cascada                                                         | 23       |

| 2.4.3    | Procesador paralelo-iterativo                                                 | 26       |

| 2.4.4    | Procesador en arreglo                                                         | 28       |

# Índice de contenido

| 2.5   | Metodología para el diseño digital                                         | 29  |

|-------|----------------------------------------------------------------------------|-----|

| 2.5   | 5.1 Método <i>buttom-up</i>                                                | 29  |

| 2.5   | 5.2 Método top-down                                                        | 30  |

| 2.6   | Lenguajes de descripción de hardware                                       | 32  |

| 2.6   | Lenguaje de descripción VHDL (VHSIC Hardware Description Language)         | 33  |

| 2.6   | 5.2 Ventajas de VHDL                                                       | 34  |

| 2.7   | Solución propuesta                                                         | 36  |

| Capít | ulo 3. Diseño de la arquitectura propuesta                                 | 38  |

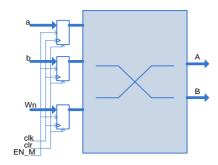

| 3.1   | Bloque de etapa de la arquitectura para evaluar la FFT                     | 38  |

| 3.2   | Bloque de memoria de datos                                                 | 41  |

| 3.2   | 2.1 Implementación de memorias FIFO para almacenamiento de datos           | 41  |

| 3.2   | 2.2 Implementación de memorias RAM para almacenamiento de datos            | 44  |

| 3.3   | Bloque de bit-reverse                                                      | 48  |

| 3.4   | Bloque generador de direcciones                                            | 49  |

| 3.5   | Bloque generador de coeficientes complejos                                 | 51  |

| 3.6   | Bloque para evaluación de la mariposa                                      | 53  |

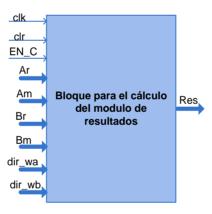

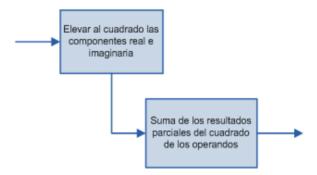

| 3.7   | Bloque para el cálculo del módulo de resultados                            | 58  |

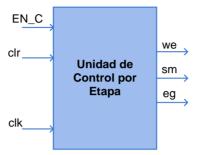

| 3.8   | Unidad de control por etapa                                                | 60  |

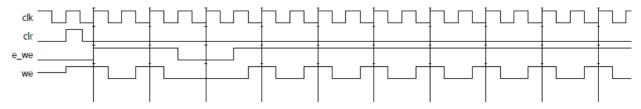

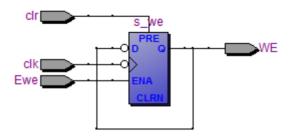

| 3.8   | 3.1 Control para la señal we                                               | 61  |

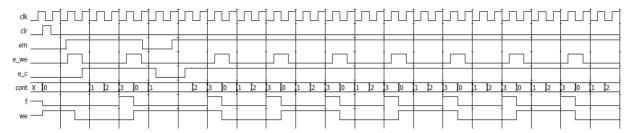

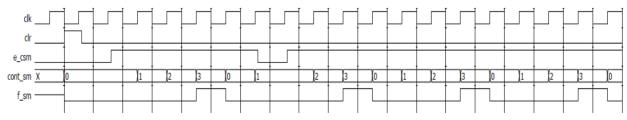

| 3.8   | 3.2 Control para la señal <i>sm</i>                                        | 65  |

| 3.8   | Control para la señal <i>eg</i> y la habilitación de <i>we</i> y <i>sm</i> | 69  |

| 3.9   | Unidad de control general                                                  | 70  |

| Capít | ulo 4. Implementación y pruebas funcionales                                | 76  |

| 4.1   | Pruebas del bloque de memoria de datos                                     | 76  |

| 4.2   | Pruebas del bloque bit-reverse                                             | 79  |

| 4.3   | Pruebas del bloque generador de direcciones                                | 81  |

| 4.4   | Pruebas del bloque generador de coeficientes complejos                     | 84  |

| 4.5   | Pruebas del bloque para la evaluación de la mariposa                       | 87  |

| 4.6   | Pruebas del bloque para el cálculo del módulo de resultados                | 94  |

| 4.7   | Pruebas de la unidad de control por etapa                                  | 98  |

| 4.7   | 7.1 Pruebas de control para la señal <i>we</i>                             | 98  |

| 4.7   | 7.2 Pruebas de control para la señal <i>sm</i>                             | 102 |

# Índice de contenido

| В.   | Cód                                                                                      | igo fuente                                                                           | 165 |

|------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|

| A.   | Prog                                                                                     | grama en C para el cálculo de la FFT                                                 | 162 |

| Refe | renci                                                                                    | as                                                                                   | 159 |

| 6.2  | Tra                                                                                      | ıbajo a futuro                                                                       | 157 |

| 6.1  |                                                                                          | nclusiones                                                                           |     |

| Capí | ítulo                                                                                    | 6. Conclusiones y trabajo a futuro                                                   | 156 |

| 5    | .4.1                                                                                     | Propuesta de medida de rendimiento                                                   | 152 |

| 5.4  | Est                                                                                      | adísticas temporales y comparación con el estado del arte                            | 149 |

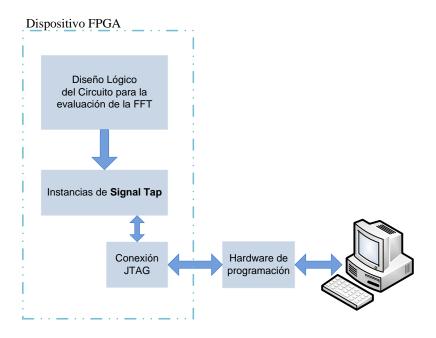

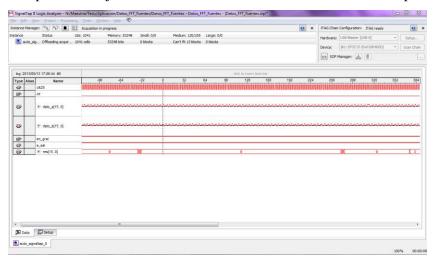

| 5.3  | Pru                                                                                      | neba del funcionamiento de la arquitectura sobre la tarjeta de desarrollo Altera-DE2 | 143 |

| 5.2  | Co                                                                                       | mparativa de los resultados hardware-software de la evaluación                       | 129 |

| 5.1  | Ar                                                                                       | quitectura para la evaluación de 512 puntos                                          | 127 |

| Capí | ítulo :                                                                                  | 5. Presentación de resultados                                                        | 127 |

| 4.10 | ) Pru                                                                                    | nebas funcionales de la arquitectura                                                 | 121 |

| 4.9  | Prı                                                                                      | nebas del bloque de etapa de la arquitectura para la evaluación de la FFT            | 112 |

| 4.8  | Pru                                                                                      | nebas de la unidad de control general                                                | 109 |

| 4    | .7.4                                                                                     | Pruebas de integración de la unidad de control por etapa                             | 107 |

| 4    | 4.7.3 Pruebas de control para la señal <i>eg</i> y habilitación de <i>we</i> y <i>sm</i> |                                                                                      | 106 |

| Fig. 1.1 Diagrama de bloques de un sistema de procesamiento digital de señales [1]             | 2  |

|------------------------------------------------------------------------------------------------|----|

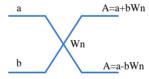

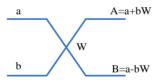

| Fig. 2.1 Mariposa para algoritmo FFT Radix-2.                                                  | 12 |

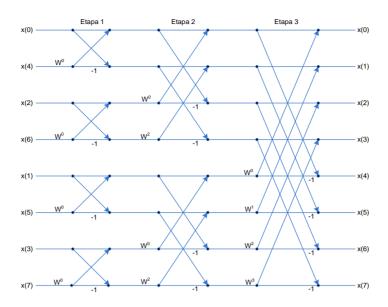

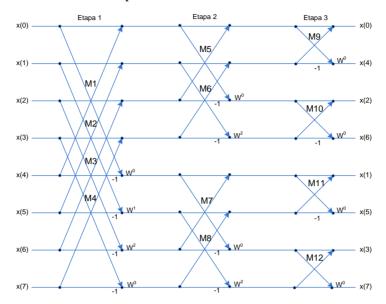

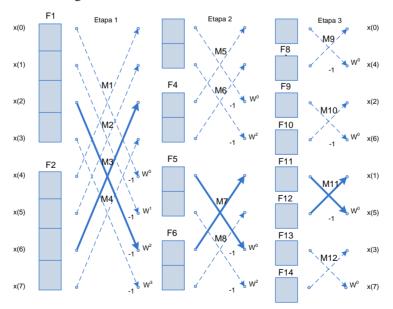

| Fig. 2.2 Algoritmo de la FFT Radix-2 [1]                                                       |    |

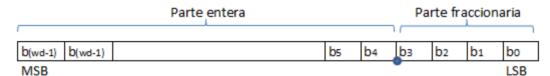

| Fig. 2.3 Representación de números en formato de punto fijo                                    |    |

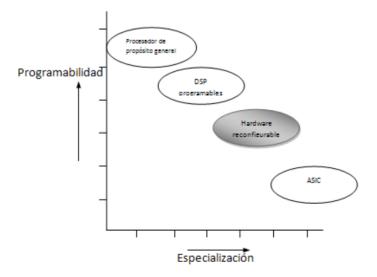

| Fig. 2.4 Espectro de implementación de algoritmos de Procesamiento Digital de Señales [8]      |    |

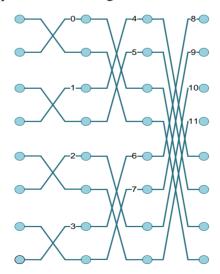

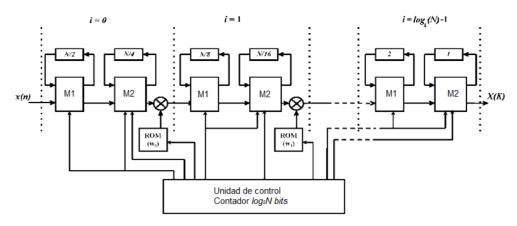

| Fig. 2.5 Evaluación de la FFT para N=8.                                                        |    |

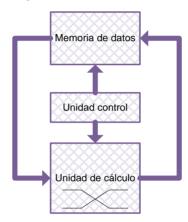

| Fig. 2.6 Esquema de procesamiento secuencial.                                                  |    |

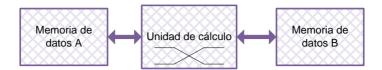

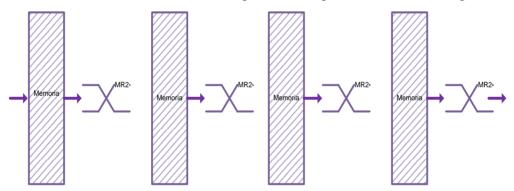

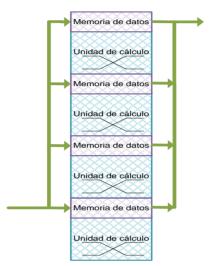

| Fig. 2.7 Esquema de procesamiento de memoria doble                                             |    |

| Fig. 2.8 Arquitectura propuesta en [12].                                                       | 22 |

| Fig. 2.9 Arquitectura propuesta en [14].                                                       |    |

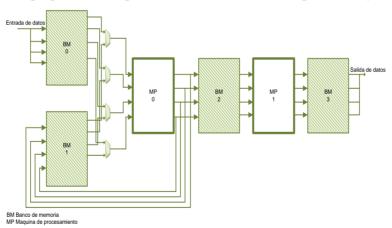

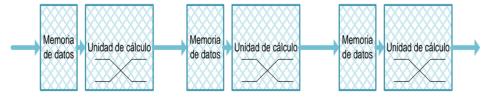

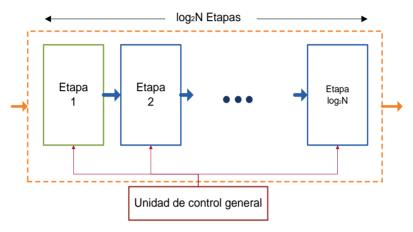

| Fig. 2.10 Esquema de procesamiento en cascada.                                                 |    |

| Fig. 2.11 Arquitectura propuesta en [18].                                                      | 24 |

| Fig. 2.12 Arquitectura propuesta en [17].                                                      |    |

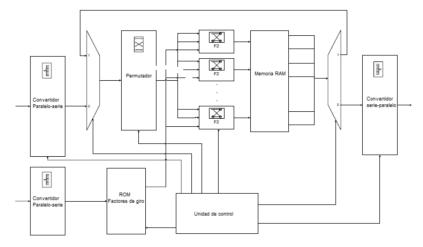

| Fig. 2.13 Arquitectura propuesta en [19].                                                      | 25 |

| Fig. 2.14 Esquema de procesamiento en paralelo-iterativo.                                      | 26 |

| Fig. 2.15 Arquitectura propuesta por [20]                                                      |    |

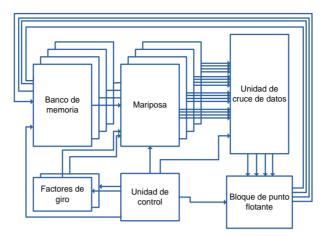

| Fig. 2.16 Arquitectura propuesta en [21].                                                      | 28 |

| Fig. 2.17 Esquema de procesamiento en arreglo                                                  | 28 |

| Fig. 2.18 Flujo general del diseño electrónico.                                                | 29 |

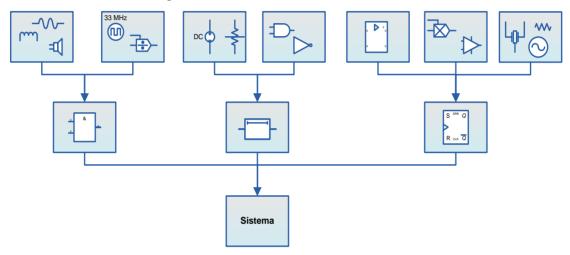

| Fig. 2.19 Método bottom-up para el diseño de circuitos                                         | 30 |

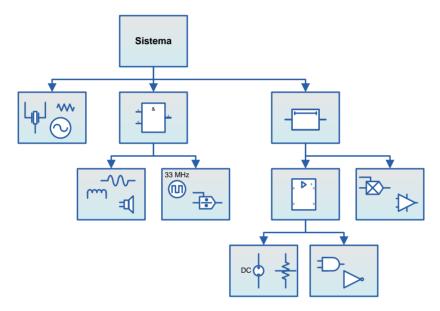

| Fig. 2.20 Método de diseño top-down.                                                           | 31 |

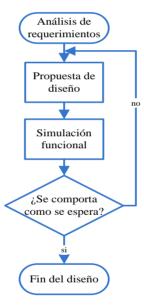

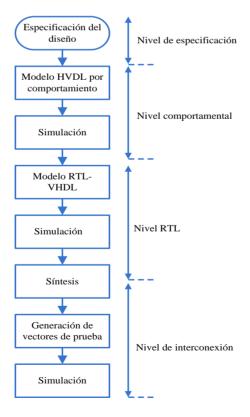

| Fig. 2.21 Flujo de diseño de un circuito en VHDL.                                              | 33 |

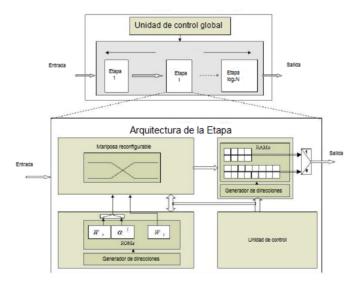

| Fig. 2.22 Diagrama general de bloques de la arquitectura propuesta.                            | 36 |

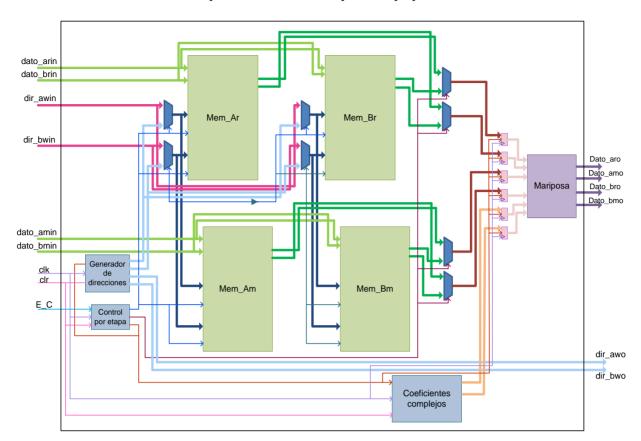

| Fig. 3.1 Bloque funcional para la evaluación de una etapa del algoritmo FFT                    | 39 |

| Fig. 3.2 Flujo de operaciones para el algoritmo de la FFT Radix-2 con decimación en frecuencia | 42 |

| Fig. 3.3 Evaluación de la FFT Radix-2 decimación en frecuencia utilizando memorias FIFO        | 43 |

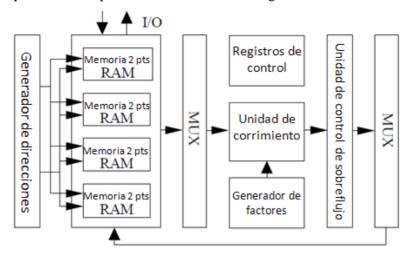

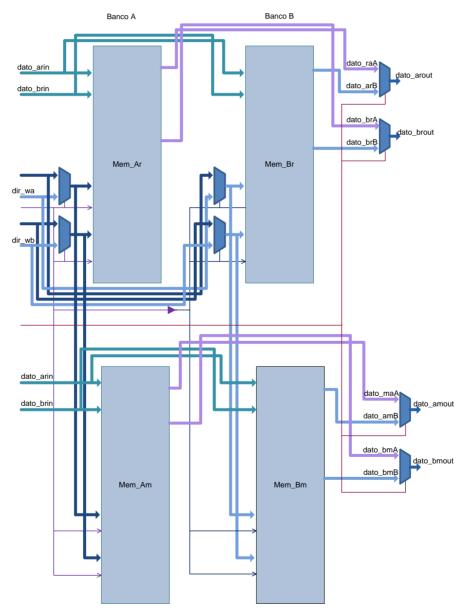

| Fig. 3.4 Diagrama de bloques de la distribución de un bloque de memoria de datos               | 45 |

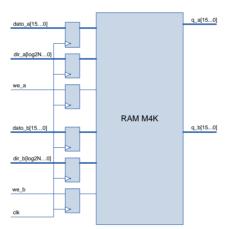

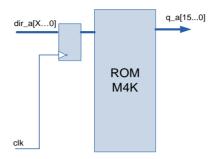

| Fig. 3.5 Configuración de Memoria M4K.                                                         | 47 |

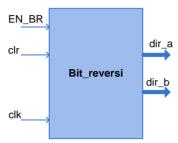

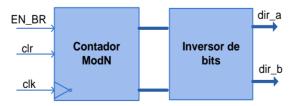

| Fig. 3.6 Entidad del bloque para bit-reverse.                                                  | 48 |

| Fig. 3.7 Diagrama de componentes del bloque bit-reverse.                                       | 48 |

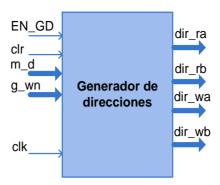

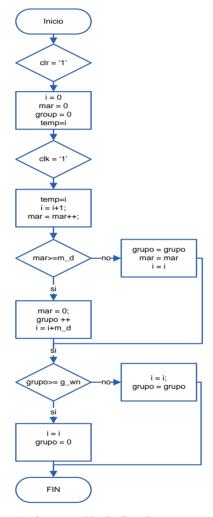

| Fig. 3.8 Entidad del bloque Generador de direcciones.                                          |    |

| Fig. 3.9 Diagrama de flujo para el algoritmo para la generación de direcciones                 | 51 |

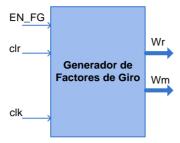

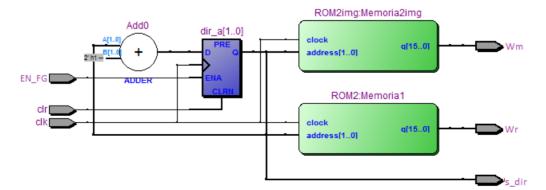

| Fig. 3.10 Entidad del Generador de coeficientes complejos.                                     |    |

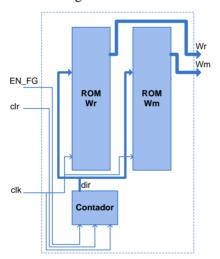

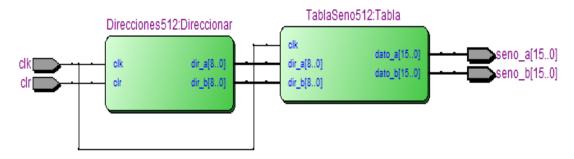

| Fig. 3.11 Diagrama de bloques del generador de coeficientes complejos.                         | 52 |

| Fig. 3.12 Configuración para el bloque M4K del bloque de memoria                               | 53 |

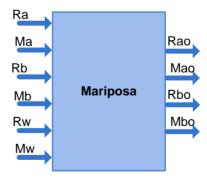

| Fig. 3.13 Entidad genérica de la mariposa.                                                     |    |

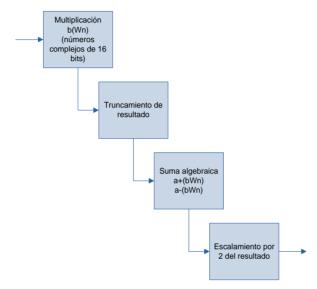

| Fig. 3.14 Flujo de operaciones de mariposa                                                     | 54 |

| Fig. 3.15 Definición de la operación mariposa para la FFT.                                     | 54 |

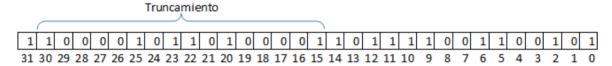

| Fig. 3.16 Truncamiento de la multiplicación.                                                             | 55 |

|----------------------------------------------------------------------------------------------------------|----|

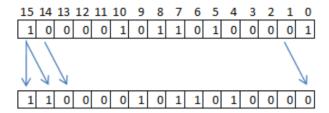

| Fig. 3.17 Escalamiento inter-etapa del resultado.                                                        | 56 |

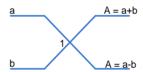

| Fig. 3.18 Definición de la mariposa para la primera etapa.                                               | 56 |

| Fig. 3.19 Diagrama de bloques de la mariposa.                                                            | 58 |

| Fig. 3.20 Entidad del bloque para el cálculo del módulo de resultados                                    | 58 |

| Fig. 3.21 Flujo de operaciones para el cálculo del módulo                                                | 59 |

| Fig. 3.22 Entidad de la unidad de control por etapa                                                      | 61 |

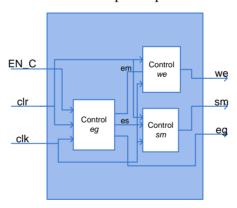

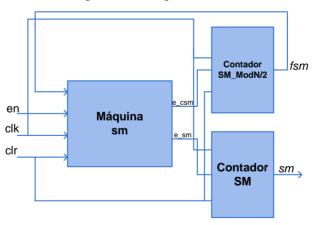

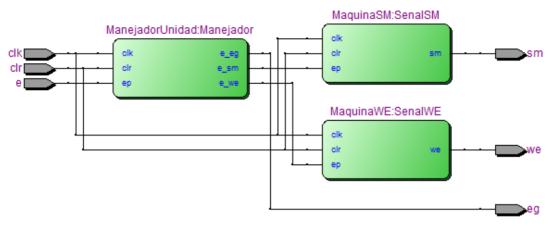

| Fig. 3.23 Diagrama de bloques de la unidad de control por etapa.                                         | 61 |

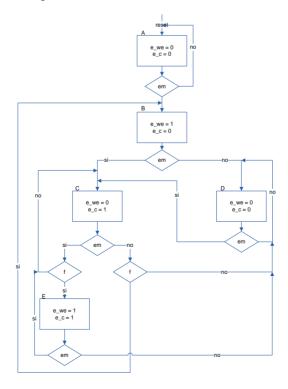

| Fig. 3.24 Carta ASM para el control de la señal WE.                                                      | 62 |

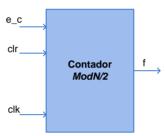

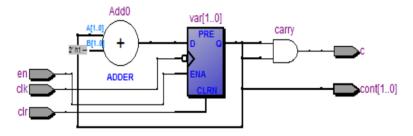

| Fig. 3.25 Entidad para el contador ModN/2                                                                | 63 |

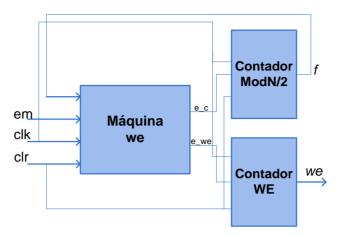

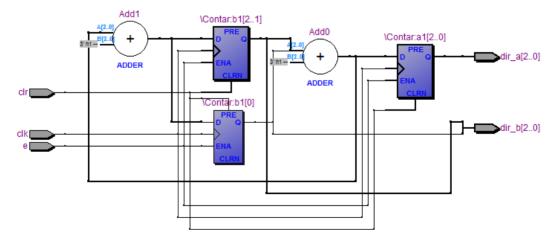

| Fig. 3.26 Diagrama de bloques del componente de control de we                                            | 64 |

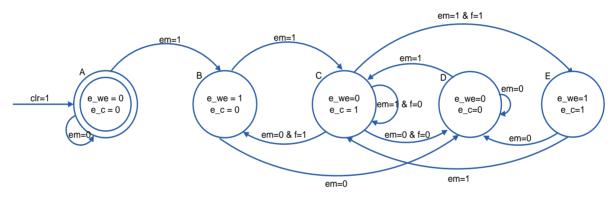

| Fig. 3.27 Máquina de estados para el manejo de la señal we                                               | 64 |

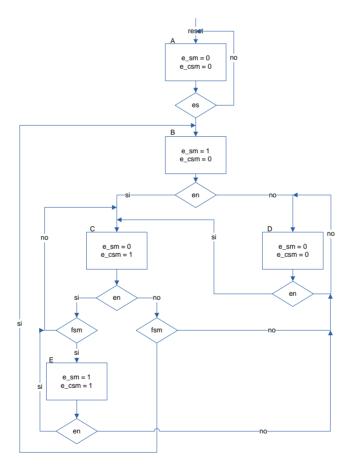

| Fig. 3.28 Carta ASM para el control de la señal sm.                                                      | 66 |

| Fig. 3.29 Diagrama de bloques de la unidad para el control de <i>sm</i>                                  |    |

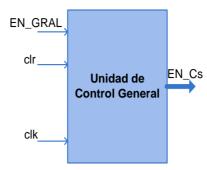

| Fig. 3.31 Entidad de la Unidad de control general.                                                       | 71 |

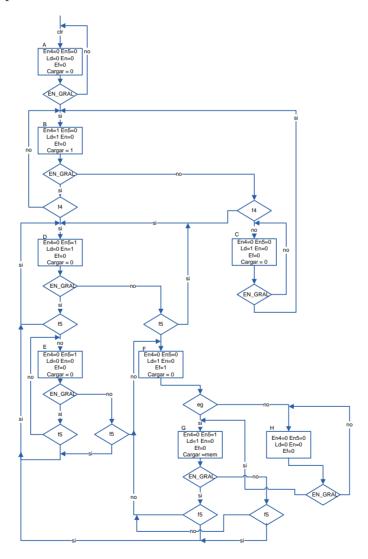

| Fig. 3.32 Carta ASM para la unidad de control general                                                    | 72 |

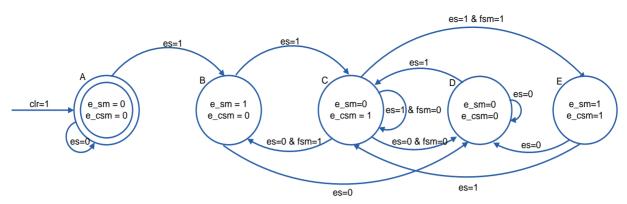

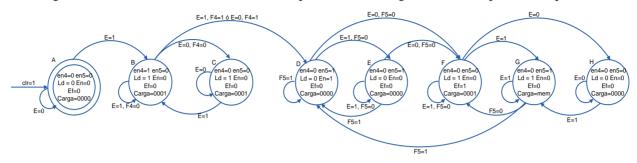

| Fig. 3.33 Máquina de estados para la unidad de control general.                                          |    |

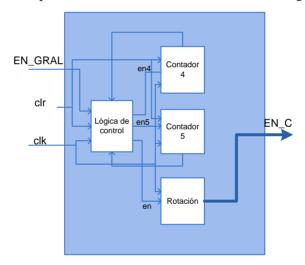

| Fig. 3.34 Diagrama de bloques de la unidad de control general                                            | 73 |

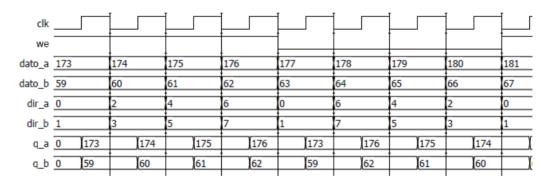

| Fig. 4.1 Simulación de la escritura de un bloque de memoria M4K                                          | 76 |

| Fig. 4.2 Simulación funcional de un banco de memoria de datos                                            | 78 |

| Fig. 4.3 Simulación funcional del bloque bit-reverse.                                                    |    |

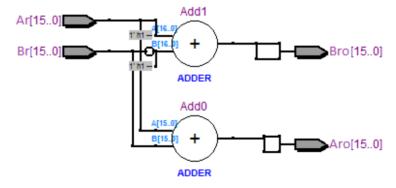

| Fig. 4.4 Diagrama RTL del bloque bit-reverse.                                                            | 81 |

| Fig. 4.5 Resultados de síntesis del bloque de bit-reverse para la arquitectura de 512 puntos             | 81 |

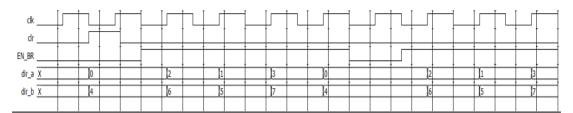

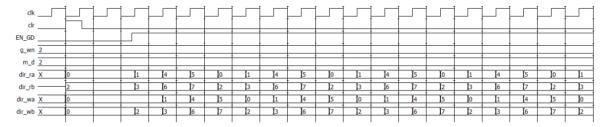

| Fig. 4.6 Simulación funcional del bloque generador de direcciones.                                       | 82 |

| Fig. 4.7 Simulación funcional para el bloque generador de direcciones de datos para la segunda etapa.    | 83 |

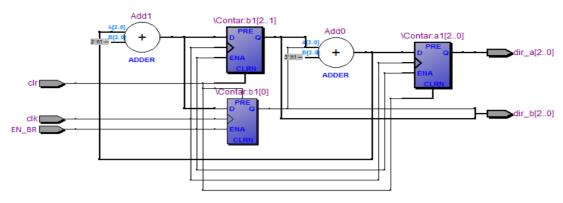

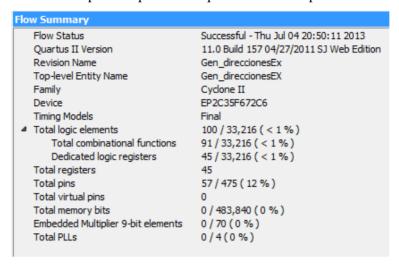

| Fig. 4.8 Diagrama RTL de Generador de direcciones.                                                       | 83 |

| Fig. 4.9 Resultados de síntesis del bloque generador de direcciones de datos                             | 84 |

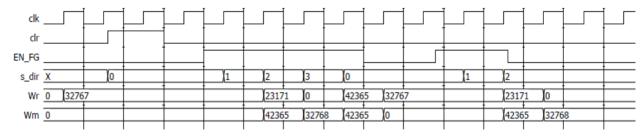

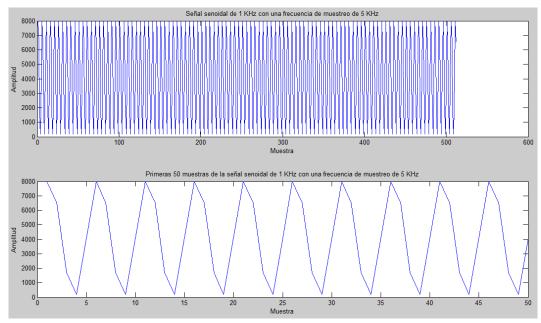

| Fig. 4.10 Simulación funcional del bloque generador de coeficientes complejos.                           | 84 |

| Fig. 4.11 Diagrama RTL del bloque generador de coeficientes complejos                                    |    |

| Fig. 4.12 Resultados de la síntesis para el bloque de coeficientes complejos de la tercera etapa de la   |    |

| arquitectura                                                                                             |    |

| Fig. 4.13 Simulación funcional del bloque para la evaluación de la mariposa de la primera etapa          | 88 |

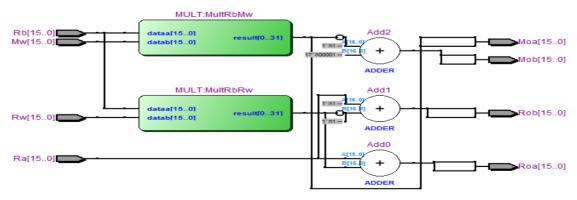

| Fig. 4.14 Diagrama <i>RTL</i> del bloque para la evaluación de la mariposa de la primera etapa           | 88 |

| Fig. 4.15 Resultados de la síntesis de la mariposa para la evaluación de la primera etapa                | 89 |

| Fig. 4.16 Simulación funcional del bloque para la evaluación de la mariposa de la segunda etapa          | 89 |

| Fig. 4.17 Diagrama <i>RTL</i> del bloque para la evaluación de la mariposa de la segunda etapa           | 90 |

| Fig. 4.18 Resultados de la síntesis del bloque para la evaluación de la mariposa de la segunda etapa     |    |

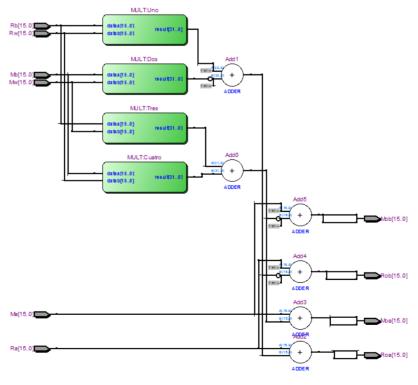

| Fig. 4.19 Simulación funcional del bloque para la evaluación de la mariposa a partir de la tercera etapa |    |

| Fig. 4.20 Diagrama RTL del bloque para la evaluación de la mariposa a partir de la tercera etapa         |    |

| Fig. 4.21 Resultados de síntesis del bloque de mariposa genérico                                         |    |

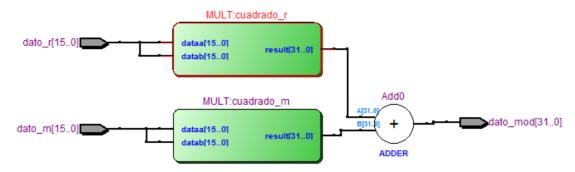

| Fig. 4.22 Simulación funcional del módulo generador de direcciones para el cálculo del módulo            | 94 |

| Fig. 4.23 Diagrama RTL del generador de direcciones para el bloque de cálculo del módulo de result                                                                                                         |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Fig. 4.24 Simulación funcional del cálculo del módulo de resultados                                                                                                                                        |        |

| Fig. 4.25 Diagrama RTL del componente para el cálculo del módulo de resultados.                                                                                                                            |        |

| Fig. 4.26 Resumen de síntesis del bloque de cálculo del módulo de resultados                                                                                                                               |        |

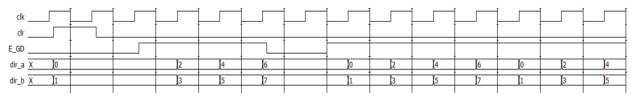

| Fig. 4.27 Simulación funcional del bloque contador para el control de la señal <i>we</i>                                                                                                                   |        |

| Fig. 4.28 Diagrama RTL del bloque contador para el control de la señal we.                                                                                                                                 |        |

| Fig. 4.29 Simulación funcional del bloque de generación de cambio de la señal we.                                                                                                                          |        |

| Fig. 4.30 Diagrama RTL del bloque de generación de cambio de la señal we                                                                                                                                   |        |

| Fig. 4.31 Simulación funcional del bloque de control para la señal <i>we</i>                                                                                                                               |        |

| Fig. 4.32 Diagrama RTL del bloque para el control de la señal we                                                                                                                                           |        |

| Fig. 4.33 Simulación funcional del bloque contador para el control de la señal <i>sm</i>                                                                                                                   |        |

| Fig. 4.34 Diagrama RTL del bloque contador para el control de la señal <i>sm.</i>                                                                                                                          |        |

| Fig. 4.35 Simulación funcional del contador <i>sm</i> .                                                                                                                                                    | 103    |

| Fig. 4.36 Diagrama RTL del bloque de generación de cambio de la señal <i>sm.</i>                                                                                                                           | 104    |

| Fig. 4.37 Simulación funcional del bloque de control para la señal sm.                                                                                                                                     |        |

| Fig. 4.38 Diagrama RTL del circuito para el control de la señal <i>sm</i>                                                                                                                                  | 106    |

| Fig. 4.39 Simulación funcional del control para la señal eg y habilitación de los bloques de control de                                                                                                    | e sm   |

| y we                                                                                                                                                                                                       | 106    |

| Fig. 4.40 Diagrama <i>RTL</i> del bloque de control para la señal <i>eg</i> y habilitación de <i>sm</i> y <i>we</i>                                                                                        | 107    |

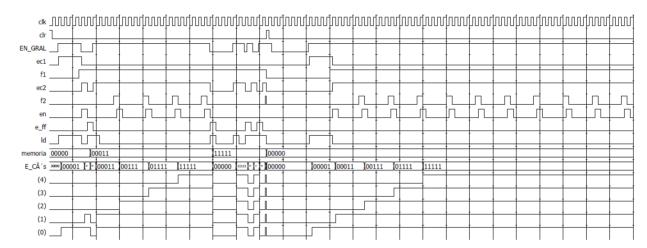

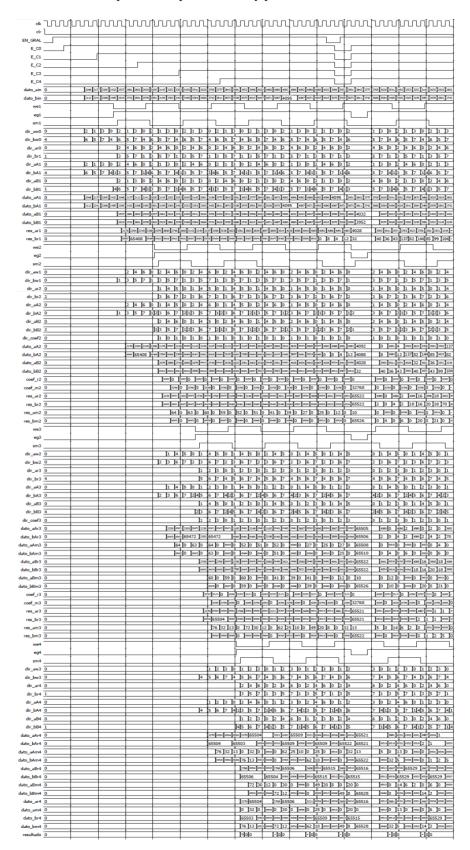

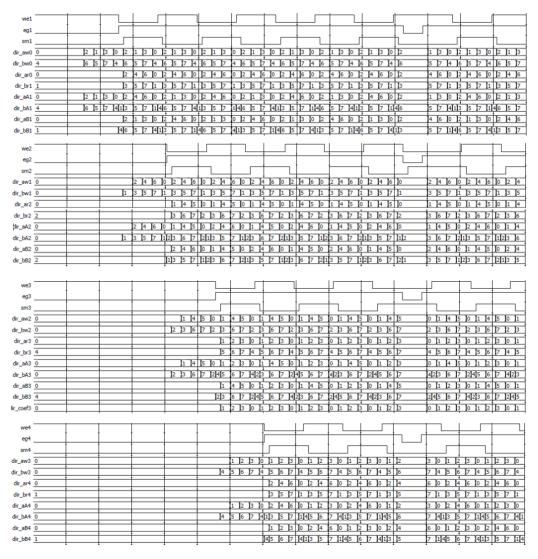

| Fig. 4.41 Simulación funcional de la unidad de control por etapa                                                                                                                                           |        |

| Fig. 4.42 Diagrama <i>RTL</i> de la unidad de control por etapa.                                                                                                                                           | 109    |

| Fig. 4.43 Resultados de síntesis de la unidad de control por etapa.                                                                                                                                        | 109    |

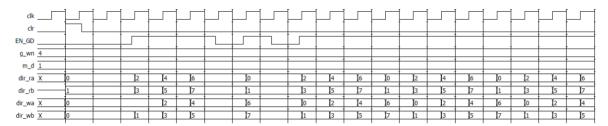

| Fig. 4.44 Simulación funcional del bloque de control general.                                                                                                                                              |        |

| Fig. 4.45 Diagrama <i>RTL</i> de la unidad de control general.                                                                                                                                             |        |

| Fig. 4.46 Resultados de la síntesis de la unidad de control general                                                                                                                                        |        |

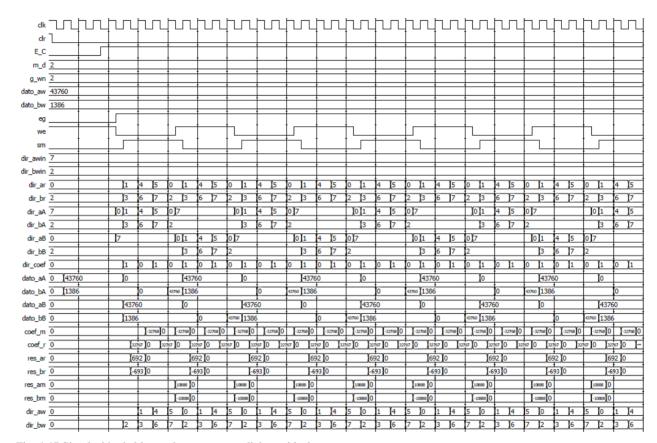

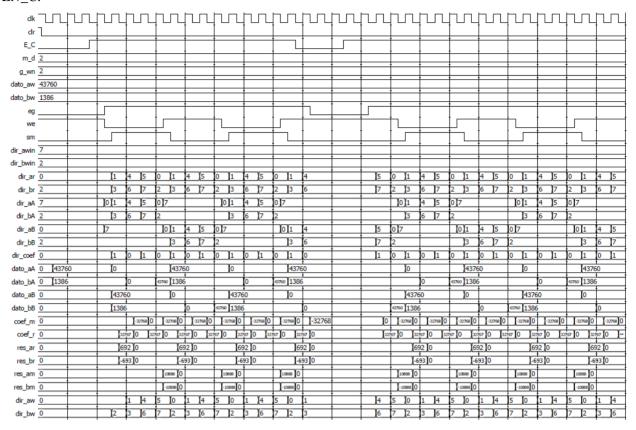

| Fig. 4.47 Simulación de bloque de etapa en condiciones ideales.                                                                                                                                            |        |

| Fig. 4.48 Simulación de bloque de etapa con interrupción en la señal <i>EN_C</i>                                                                                                                           | 118    |

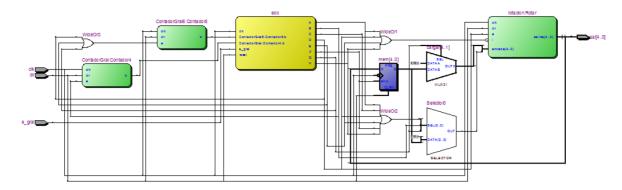

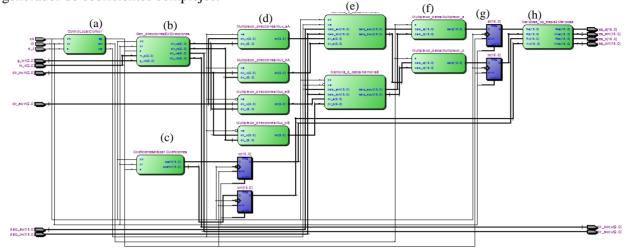

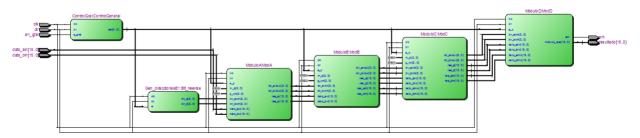

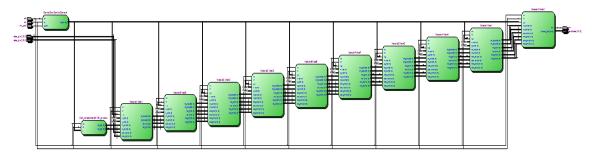

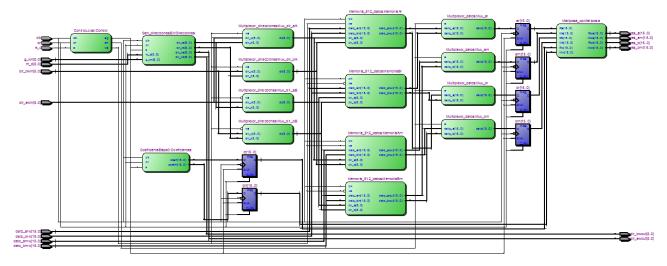

| Fig. 4.49 Diagrama del circuito resultante de la síntesis del bloque de evaluación de una etapa de la arquitectura para evaluar la FFT (a) Unidad de control por etapa (b) Bloque generador de direcciones | s de   |

| datos (c) Bloque generador de coeficientes complejos (d) Multiplexores de direcciones (e) Bloques d                                                                                                        |        |

| memorias de datos (f) Multiplexores de datos (g) Registros de mariposa (h) Bloque para la evaluació                                                                                                        |        |

| la mariposa.                                                                                                                                                                                               |        |

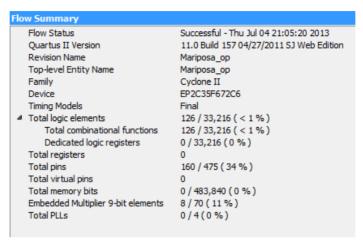

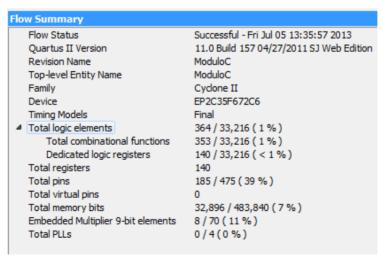

| Fig. 4.50 Resultados de la síntesis para la tercera etapa de la arquitectura                                                                                                                               |        |

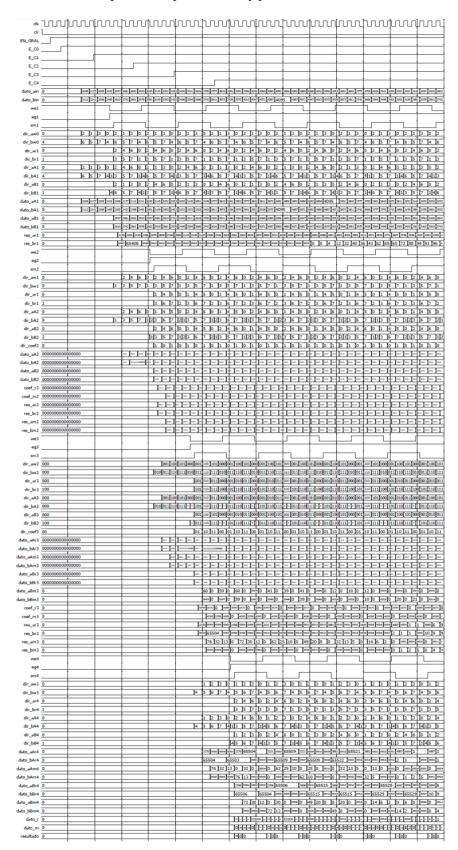

| Fig. 4.51 Simulación funcional de la arquitectura.                                                                                                                                                         |        |

| Fig. 4.52 Simulación de la arquitectura completa para la evaluación del algoritmo con una interrupcion                                                                                                     |        |

| EN_GRAL.                                                                                                                                                                                                   |        |

| Fig. 4.53 Verificación de la selección de las direcciones de lectura/escritura de las memorias de datos                                                                                                    | s. 125 |

| Fig. 4.54 Diagrama RTL del circuito resultante de la arquitectura para la evaluación de la FFT de 8                                                                                                        |        |

| puntos.                                                                                                                                                                                                    | 126    |

|                                                                                                                                                                                                            |        |

|                                                                                                                                                                                                            |        |

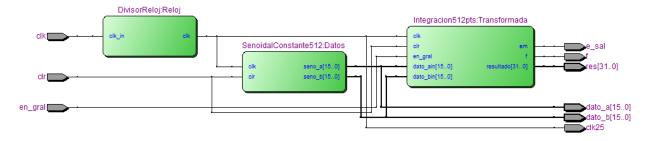

| Fig. 5.1 Diagrama RTL de la arquitectura para el cálculo de la FFT de 512 puntos.                                                                                                                          |        |

| Fig. 5.2 Diagrama RTL del circuito para la evaluación de una etapa de la FFT de 512 puntos                                                                                                                 | 128    |

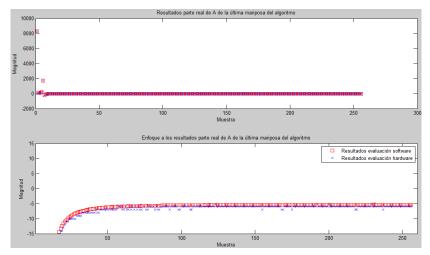

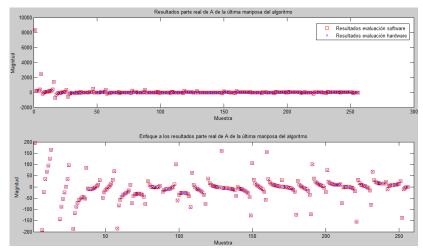

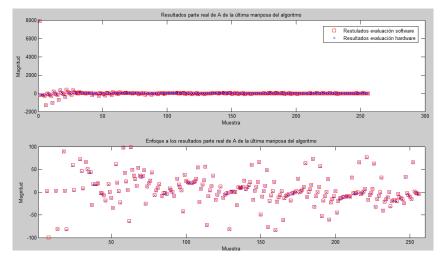

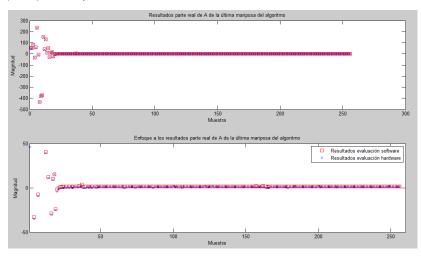

| Fig. 5.3 Resultado parte real de A de la mariposa de la última etapa de evaluación de la señal senoidal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .130  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

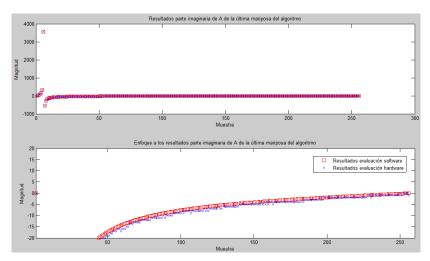

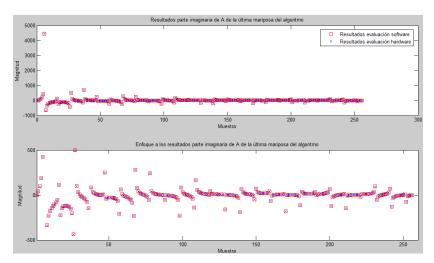

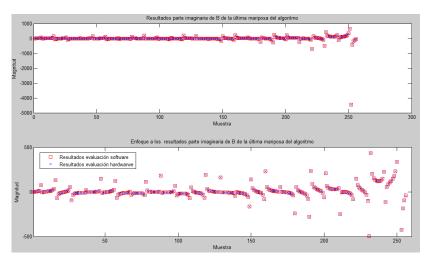

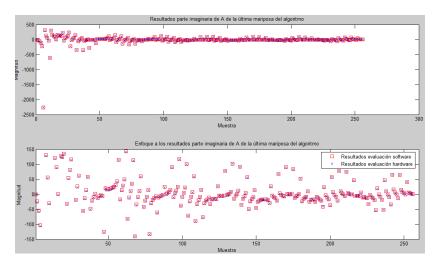

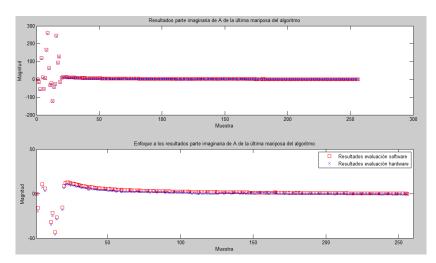

| Fig. 5.4 Resultado parte imaginaria de A de la mariposa de la última etapa de evaluación de la señal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| senoidal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 130 |

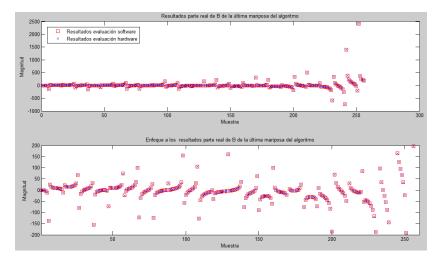

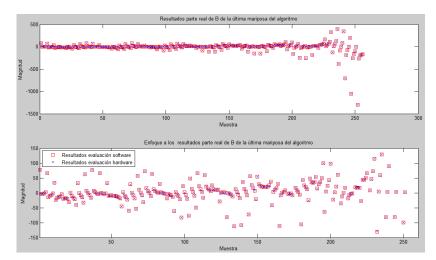

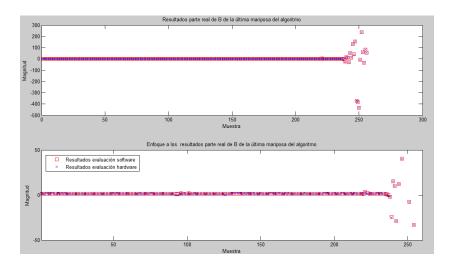

| Fig. 5.5 Resultado parte real de B de la mariposa de la última etapa de evaluación de la señal senoidal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .131  |

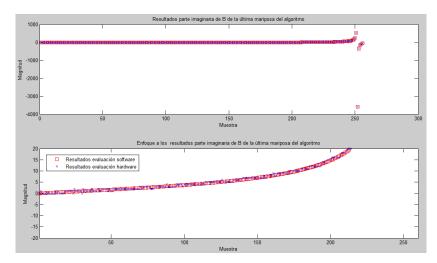

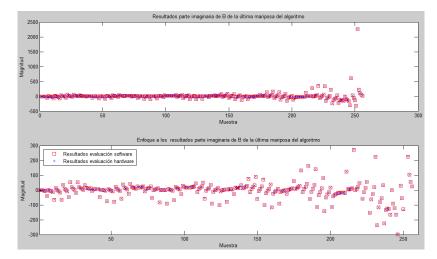

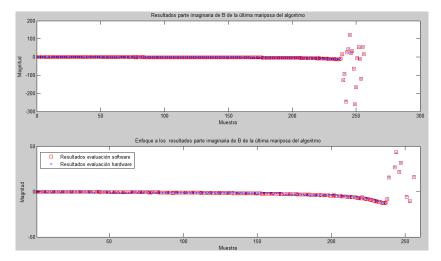

| Fig. 5.6 Resultado parte imaginaria de B de la mariposa de la última etapa de evaluación de la señal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| senoidal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 131 |

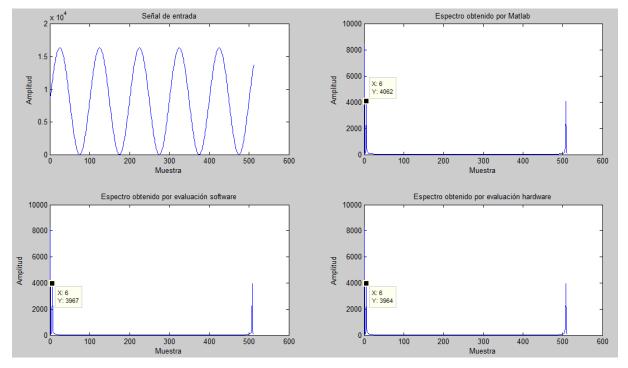

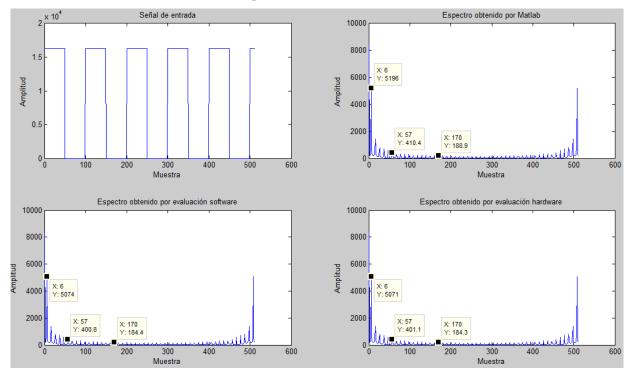

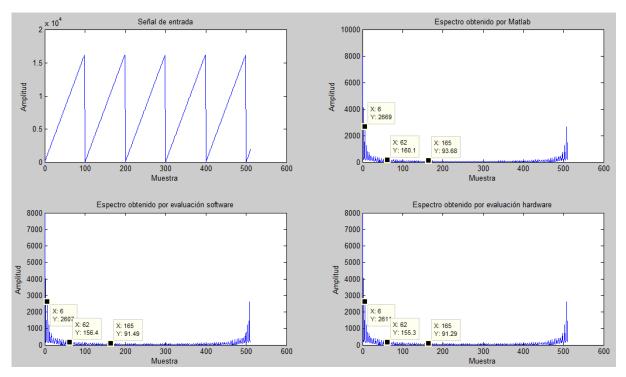

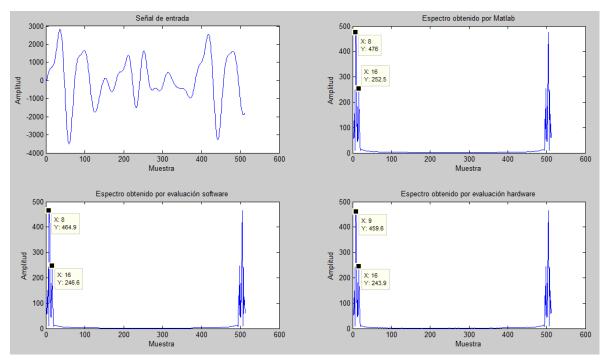

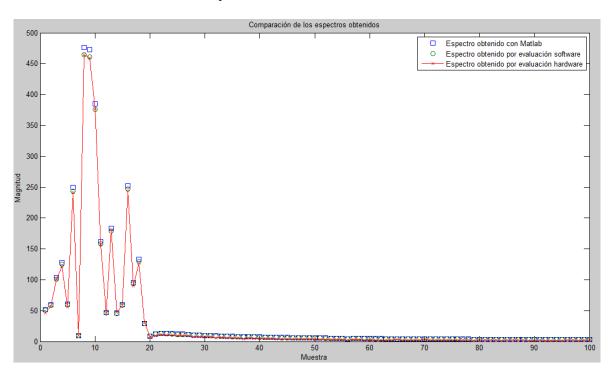

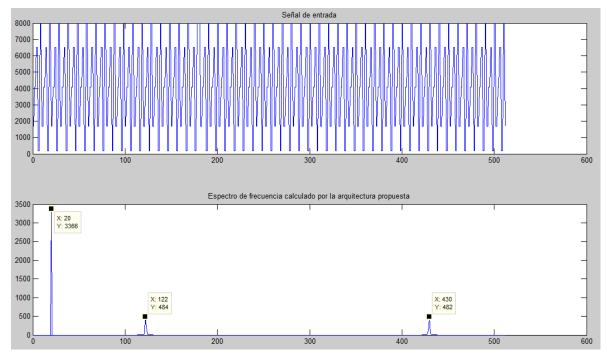

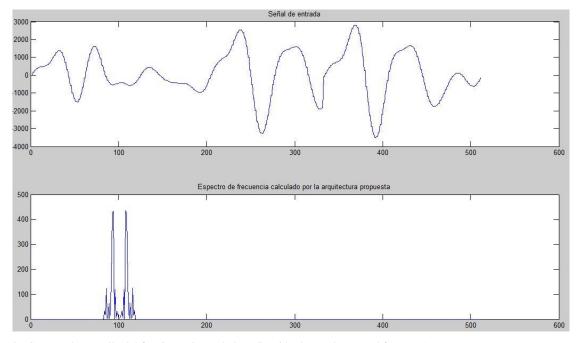

| Fig. 5.7 Comparativa de los resultados para la señal senoidal de entrada.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 132 |

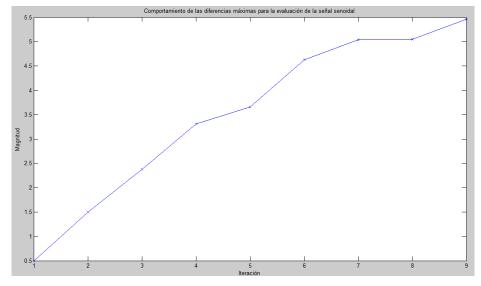

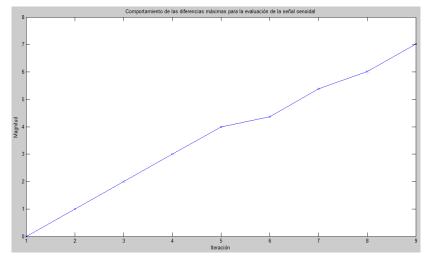

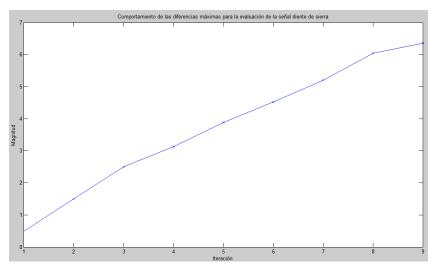

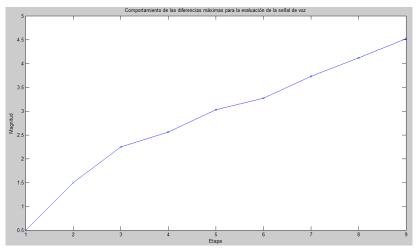

| Fig. 5.8 Evolución de las diferencias para la evaluación software vs hardware con entrada de señal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| senoidal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 132 |

| Fig. 5.9 Resultado parte real de A de la mariposa de la última etapa de evaluación de la señal cuadrada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | a.    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| Fig. 5.10 Resultado parte imaginaria de A de la mariposa de la última etapa de evaluación de la señal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| cuadrada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .134  |

| Fig. 5.11 Resultado parte real de B de la mariposa de la última etapa de evaluación de la señal cuadrac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

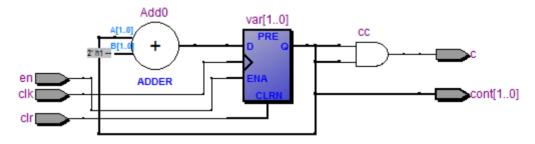

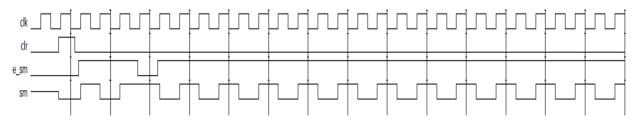

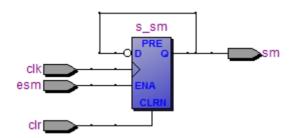

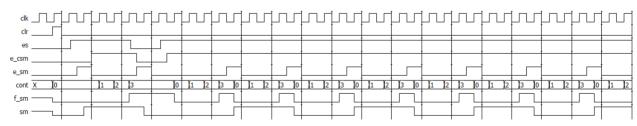

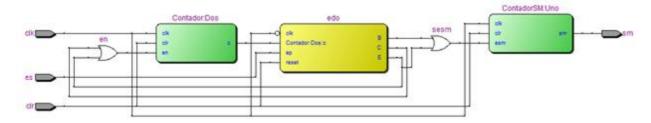

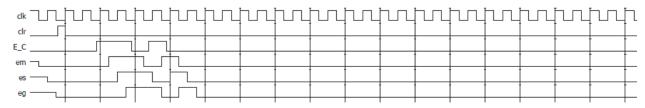

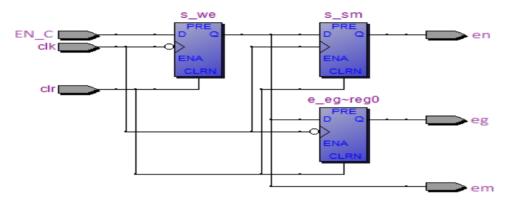

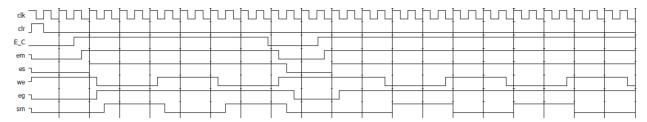

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |