# INSTITUTO POLITÉCNICO NACIONAL

#### CENTRO DE INVESTIGACIÓN EN COMPUTACIÓN

# DETECCIÓN, PREDICCIÓN Y EJECUCIÓN DE OPERACIONES REDUNDANTES PARA INCREMENTAR EL RENDIMIENTO DE UN MICROPROCESADOR

### **TESIS**

QUE PARA OBTENER EL GRADO DE MAESTRO EN CIENCIAS EN INGENIERÍA DE CÓMPUTO CON ESPECIALIDAD EN SISTEMAS DIGITALES

#### PRESENTA:

ING. ALEJANDRO VILLAR BRIONES

DIRECTOR: DR. LUIS ALFONSO VILLA VARGAS

CODIRECTOR: DR. OSCAR CAMACHO NIETO

MÉXICO, D.F.

**OCTUBRE DEL 2003**

### Dedicatoria

A mis Padres quienes lo han dado todo por que alcance mi realización como persona, profesionista e hijo; siempre sin esperar nada a cambio por tan valioso legado y apoyo. A ellos todo mi amor y cariño.

A mis hermanos Claudia, Fabiola y Armando, por el apoyo incondicional que siempre me han dado y estar conmigo en todo momento de mi vida.

A mis abuelos maternos Consuelo y Elías, de quienes herede gran parte de mi personalidad.

A mis abuelos paternos Angélica y Luis, por todo su cariño.

A mis tíos Guadalupe, Lucina, Lourdes, Elena, Patricia, Felipe y José, de quienes he aprendido el valor del cariño de la familia, el duro esfuerzo, y su amor incondicional.

A mis tíos Luis, Erasmo, Nancy, Salvador, Emmanuel, Rosario, Thomas, Ismael Alejandro y Juan Carlos, por su comprensión e impulso que me han dado.

A todos mis amigos, con quienes he compartido las alegrías y tristezas de mi vida.

A todos ellos brindo este logro mas en mi vida.

# Agradecimientos

Al M. en C. Enrique López Guzmán por los consejos y la orientación que me dio durante la carrera.

### Al Centro de Investigación en Computación (CIC)

Al Dr. Luis Alfonso Villa Vargas, por los conocimientos transmitidos y recomendaciones para la realización de este trabajo.

Al Dr. Oscar Camacho Nieto, por su dirección y apoyo brindado para completar esta tesis.

A todos los profesores y miembros del jurado por el tiempo y esfuerzo que dedican a nuestra superación.

A todos mis compañeros por su valiosa amistad y consejos.

#### Al Instituto Mexicano del Petróleo (IMP)

En especial al Programa de Matemáticas Aplicadas y Computación (PMAyC) por la por el apoyo que me brindó para la realización de este trabajo, el equipo de computo utilizado y el uso de sus instalaciones.

A la competencia de Tecnologías de Información por el apoyo brindado y al Instituto por la beca concedida para concluir esta tesis.

# Índice

| Índice                                                                         | i              |

|--------------------------------------------------------------------------------|----------------|

| Lista de Figuras                                                               | iii            |

| Lista de Tablas                                                                | vi             |

| Resumen                                                                        | vii            |

| Abstract                                                                       | vii            |

|                                                                                |                |

| Introducción                                                                   | ix             |

| Antecedentes                                                                   | xiii           |

| Descripción y definición del problema                                          | xiv            |

| Objetivos                                                                      | xv             |

| Justificación                                                                  | xvi            |

|                                                                                |                |

| Capítulo 1. Microarquitectura de procesadores superescalares                   | 1              |

| 1.1 Introducción                                                               | 1              |

|                                                                                |                |

| 1.2 Microarquitectura típica de un procesador superescalar                     |                |

| 1.2.1 Búsqueda de instrucciones y predicción de saltos                         |                |

| 1.2.2 Decodificación, renombramiento y despacho de instrucciones               |                |

| 1.2.2.1 Tipos de dependencias                                                  |                |

| 1.2.2.2 Despacho de instrucciones                                              |                |

| 1.2.2.3 Renombramiento de registros                                            |                |

| 1.2.3 Lanzamiento de instrucciones y ejecución en paralelo                     |                |

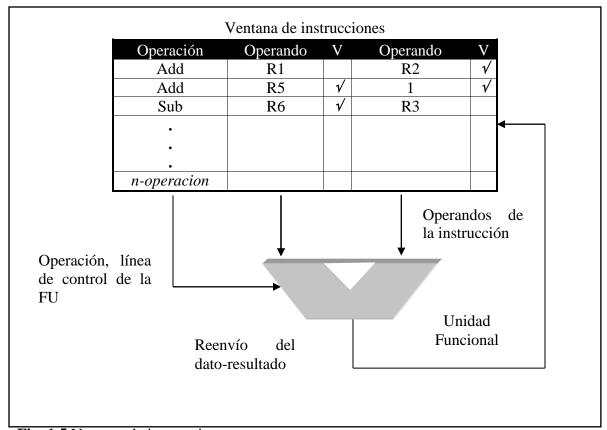

| 1.2.3.1 Estructura básica de la ventana de instrucciones o estación de reserva |                |

| 1.2.4 Operaciones de manejo de memoria                                         |                |

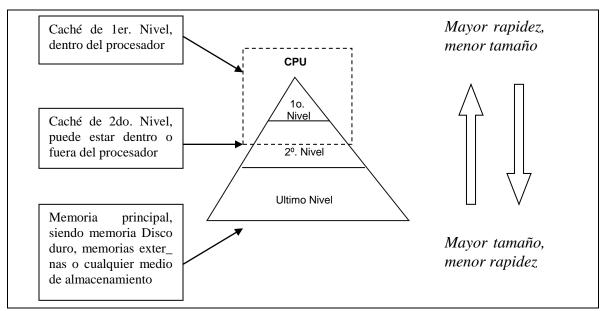

| 1.2.4.1 Memorias Caché                                                         |                |

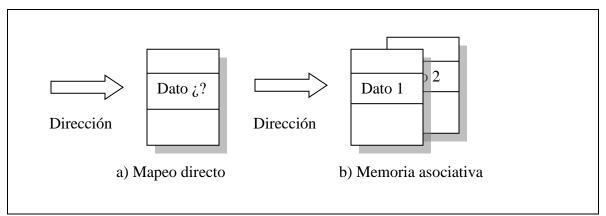

| 1.2.4.2 Localización de datos                                                  |                |

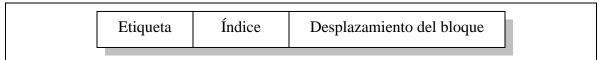

| 1.2.4.3 Políticas de reemplazo                                                 |                |

| 1.2.4.4 Tipos de fallos                                                        |                |

| 1.2.5 Retiro de instrucciones                                                  | 19             |

| 1.3 El papel del software                                                      | 20             |

| 1.4 Operaciones repetitivas en un procesador superescalar                      | 21             |

| 1.5 Análisis y modelado matemático del tiempo de ejecución                     | 23             |

| 1.5.1 Aproximación analítica                                                   | 25             |

|                                                                                |                |

| Capítulo 2. Metodología de evaluación                                          | 31             |

| 2.1 Resumen                                                                    | 31             |

| 2.2 Herramientas de simulación                                                 |                |

| 2.2.1 Resumen de simuladores de arquitecturas de microprocesadores             |                |

| 2.2.2 Selección de la Herramienta de simulación                                |                |

| 2.2.3 Modificación de la herramienta de simulación                             |                |

| 2.3 Cargas de trabajo ( <i>Benchmark</i> )                                     |                |

| 2.4 Plataforma de cómputo                                                      |                |

| <b>4.</b> ≒ 1 1atan∪ima ut computo                                             | <del>4</del> 0 |

| 2.5 Opciones de configuración para simulación de modelos                          | 40  |

|-----------------------------------------------------------------------------------|-----|

| Capítulo 3. Ejecución de instrucciones fuera de orden                             | 43  |

| 3.1 Introducción                                                                  | 43  |

| 3.2 Comportamiento de la ventana de instrucciones                                 | 43  |

| 3.2.1 Análisis de dependencias por datos en la ventana de instrucciones           |     |

| 3.2.2 Políticas de comparación de entradas dentro de la ventana de                |     |

| instrucciones                                                                     | 47  |

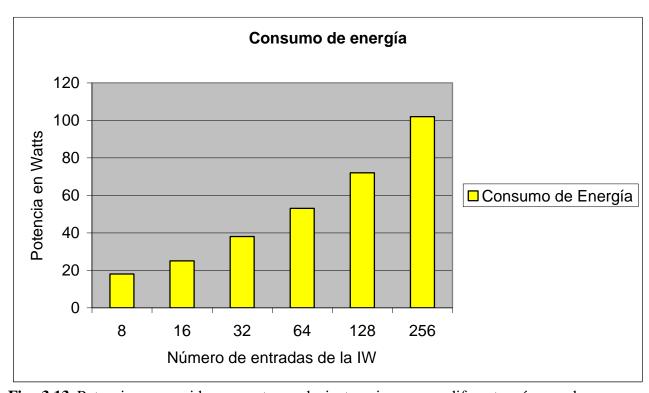

| 3.2.3 Consumo de energía                                                          |     |

| 3.3. Antecedentes                                                                 |     |

| 3.4 Ventana de instrucciones dividida en bloques                                  |     |

| 3.4.1 Submodelos de la ventana de instrucciones dividida en bloques               |     |

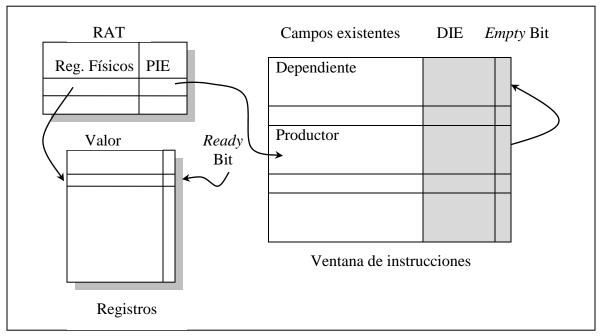

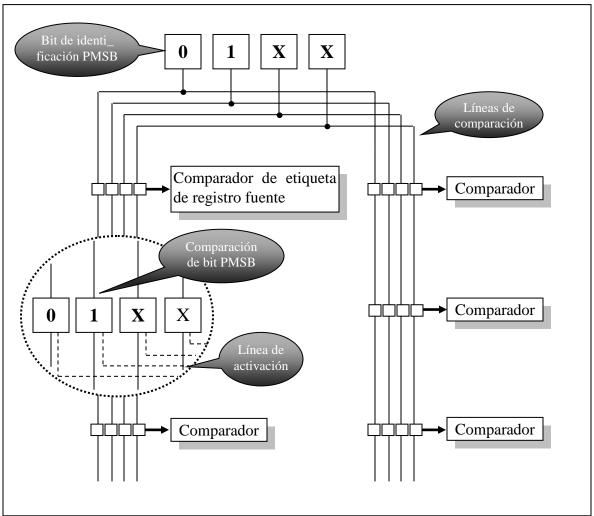

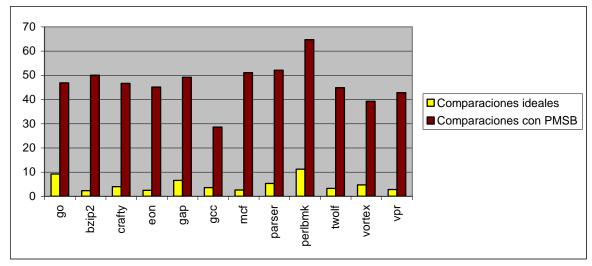

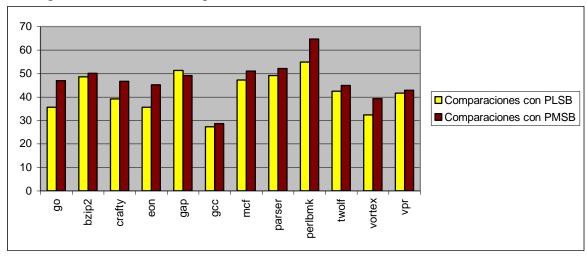

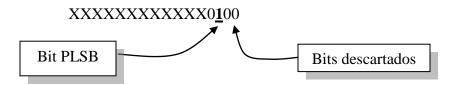

| 3.5 Ventana de instrucciones con detección de operandos por bit de identificación |     |

| 3.6 Comparación y evaluación de modelos propuestos                                |     |

| 3.0 Comparación y evariación de modelos propaestos                                | 01  |

| Capítulo 4. Sistema de Memoria                                                    | 83  |

| 4.1 Introducción                                                                  | 83  |

| 4.2 Antecedentes                                                                  | 83  |

| 4.2.1 Predicción en memorias caché                                                | 83  |

| 4.2.2 Mecanismos para mejorar el acceso a la memoria caché de datos               | 85  |

| 4.3 Manejo de operaciones redundantes en la memoria caché                         |     |

| 4.4 Detección de comportamiento                                                   | 89  |

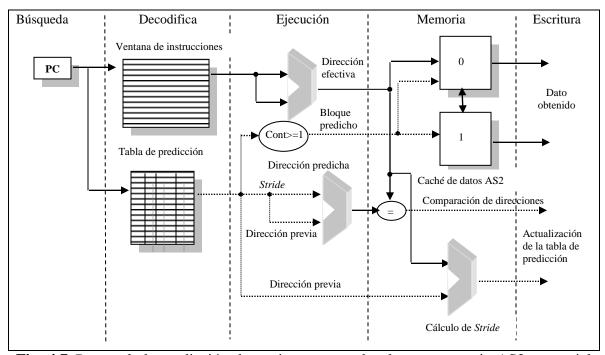

| 4.5 Caché de acceso predictivo a arreglos ( <i>PAAC</i> )                         |     |

| 4.5.1 Tabla de referencia de predicción                                           |     |

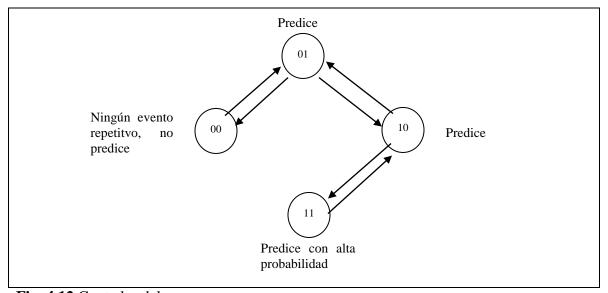

| 4.5.2 Mecanismo de predicción en base a <i>stride</i>                             |     |

| 4.5.3 Metodología de Evaluación                                                   |     |

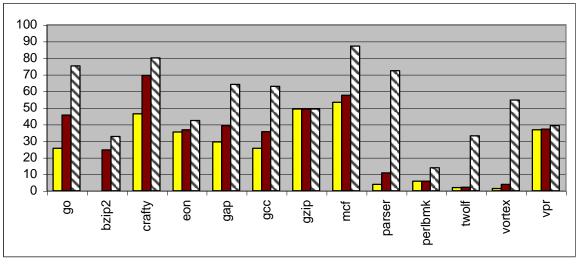

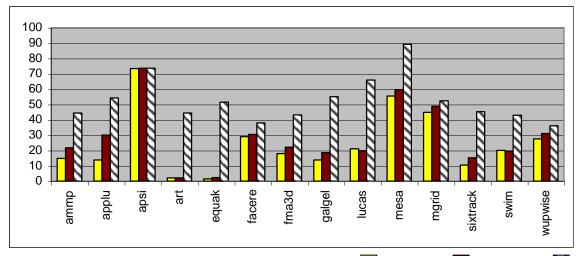

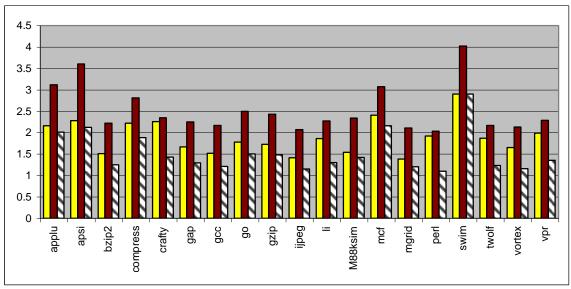

| 4.5.4 Resultados                                                                  |     |

| Capítulo 5. Conclusiones y trabajos futuros                                       | 100 |

| 5.1 Conclusión                                                                    | 100 |

| 5.2 Comentarios                                                                   | 100 |

| 5.3 Trabajos futuros                                                              | 101 |

| Referencias                                                                       | 103 |

| Introducción                                                                      | 103 |

| Capítulo 1                                                                        |     |

| Capítulo 2                                                                        |     |

| Capítulo 3                                                                        |     |

| Capítulo 4                                                                        |     |

| Capítulo 5                                                                        |     |

| Apéndice A. Símbolos                                                              | 112 |

# Lista de Figuras

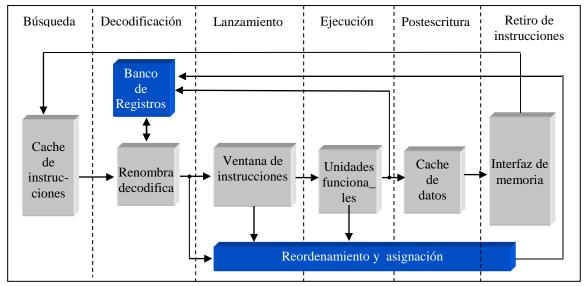

| Figura 1.1 Etapas de procesamiento de un procesador súper escalar                    | 2               |

|--------------------------------------------------------------------------------------|-----------------|

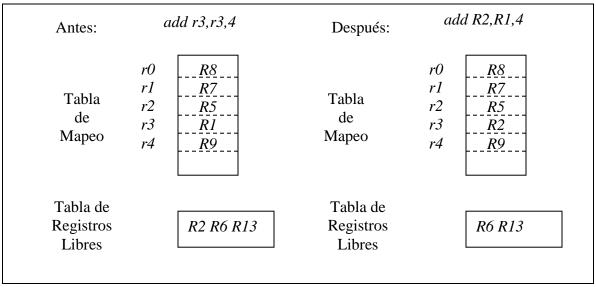

| Figura 1.2. Renombramiento de registro. Archivo de registro de renombramiento        | 7               |

| Figura 1.3. Renombramiento de registro. Reorder Buffer                               |                 |

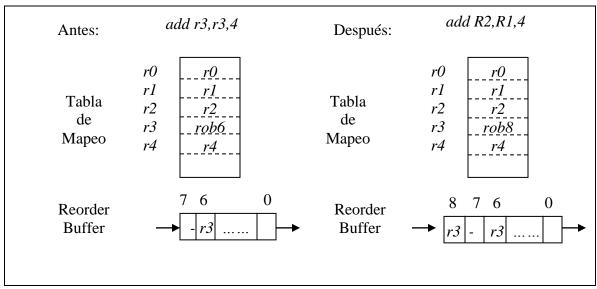

| Figura 1.4 Método de enfilamiento                                                    | 10              |

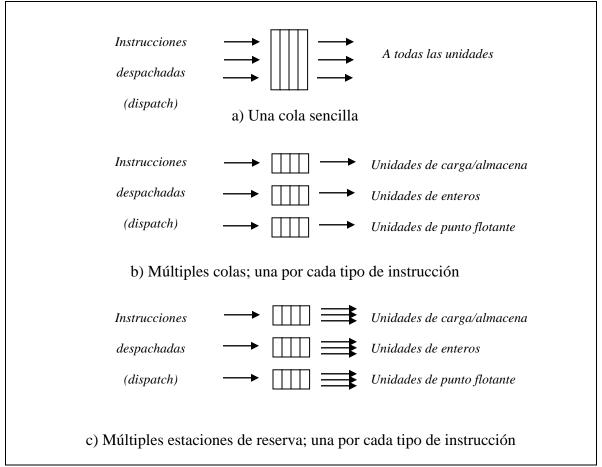

| Figura 1.5 Ventana de instrucciones                                                  | 12              |

| Figura 1.6 Jerarquía de Memoria.                                                     | 14              |

| Figura 1.7 Direccionamiento de la memoria caché                                      | 16              |

| Figura 1.8 Campos de la dirección de memoria                                         | 17              |

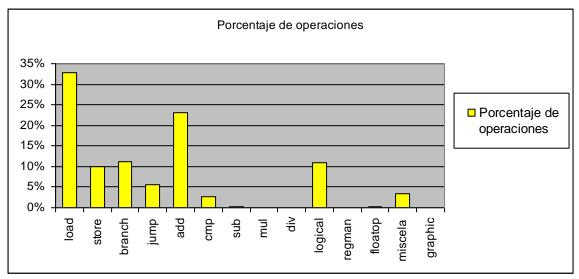

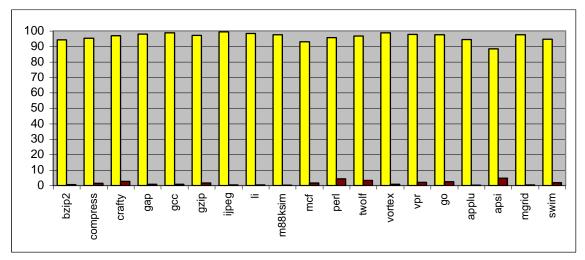

| Figura 1.9 Porcentaje de instrucciones promedio en una carga de trabajo típica       | 22              |

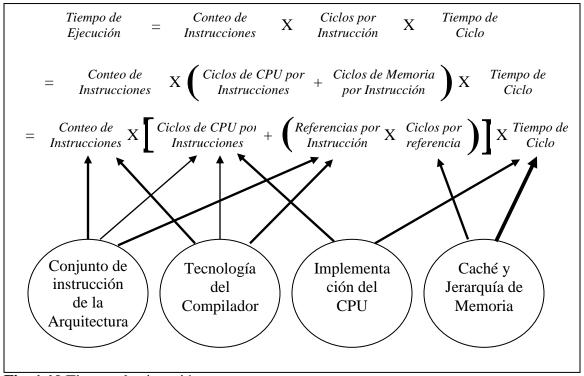

| Figura 1.10 Tiempo de ejecución                                                      | 23              |

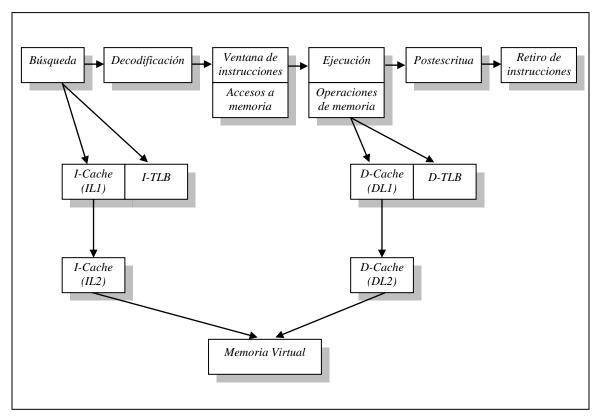

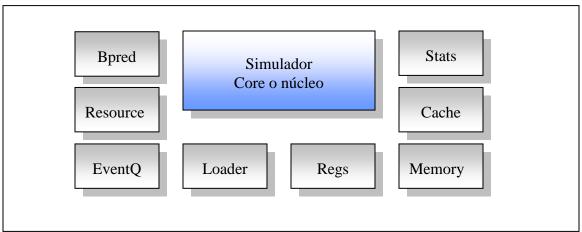

| Figura 2.1 Diagrama esquemático del simulador "sim-outorder" del Simplescalar        | 35              |

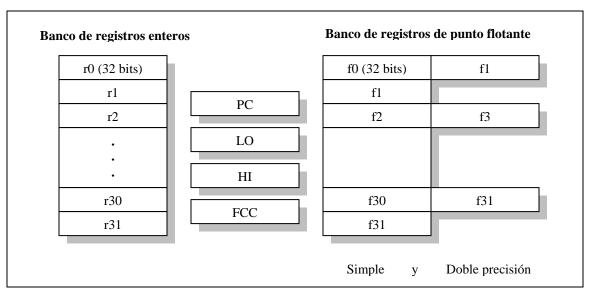

| Figura. 2.2 Bloques de registros enteros y de punto flotante de la arquitectura simu | ulada           |

| por "sim-outorder"                                                                   |                 |

| Figura 2.3 Módulos que conforman el simulador "Sim-Outorder"                         |                 |

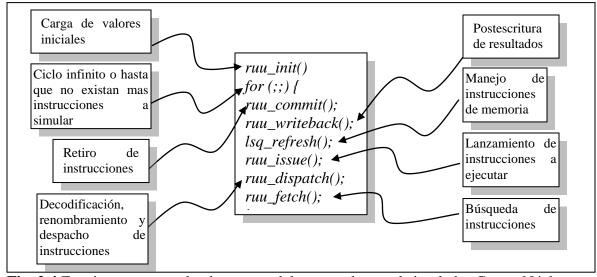

| Figura 2.4 Funciones que emulan las etapas del procesador en el simulador "          |                 |

| Outorder"                                                                            |                 |

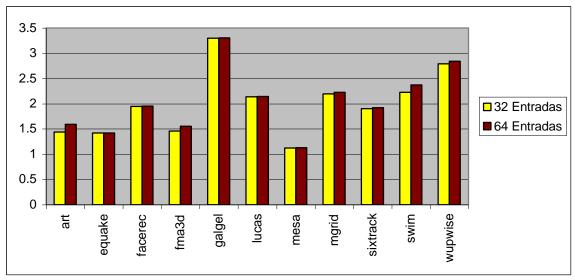

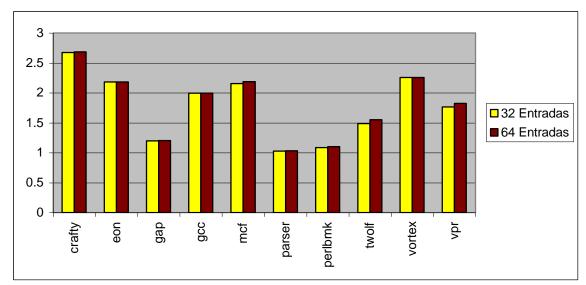

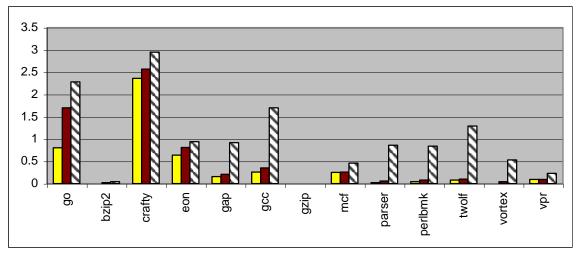

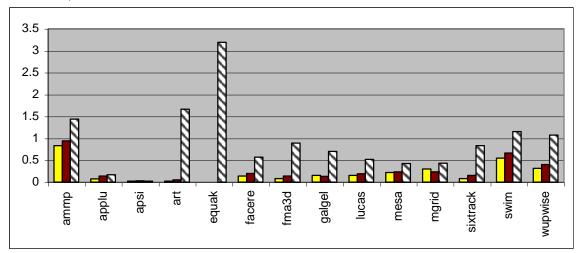

| Figura 3.1 Instrucciones por ciclo, SPECINT                                          |                 |

| Figura 3.2 Instrucciones por ciclo, SPECFP                                           | 44              |

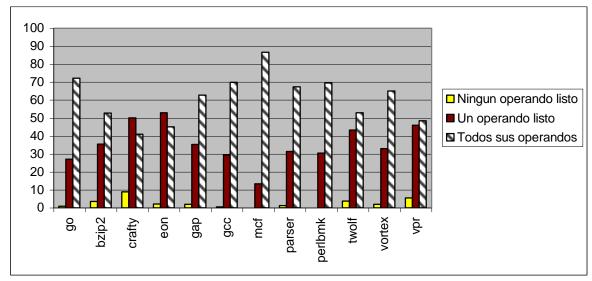

| Figura 3.3 Porcentaje de operandos fuente para enteros                               | 45              |

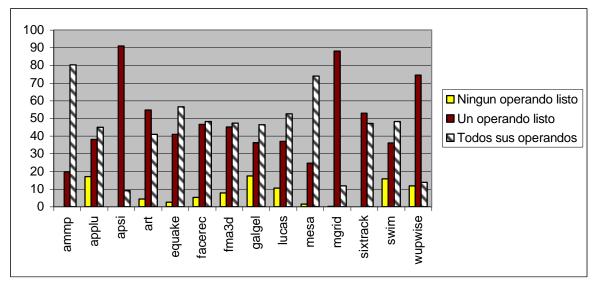

| Figura 3.4 Porcentaje de operandos fuente para flotantes                             |                 |

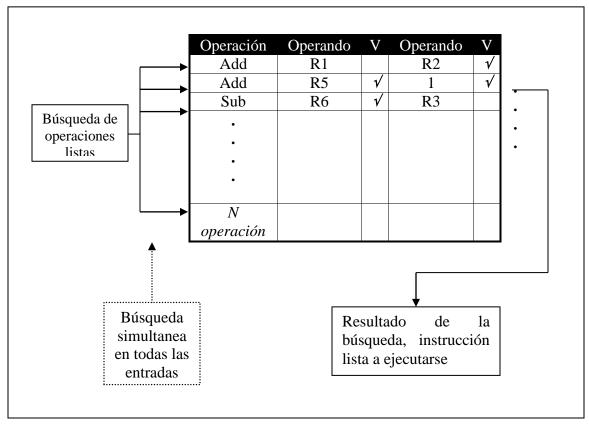

| Figura 3.5 Búsqueda de instrucciones listas para ejecutarse dentro de la ventan      |                 |

| instrucciones                                                                        |                 |

| Figura 3.6 Ventana de instrucciones de 64 entradas                                   |                 |

| Figura 3.7 Ventana de instrucciones de 32 entradas                                   |                 |

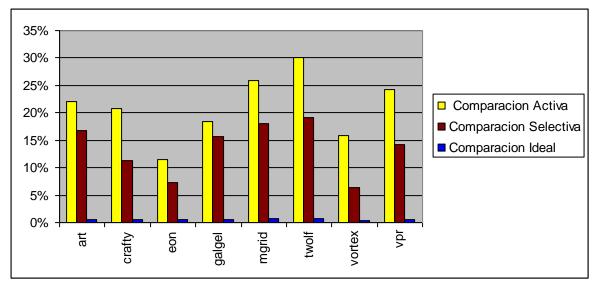

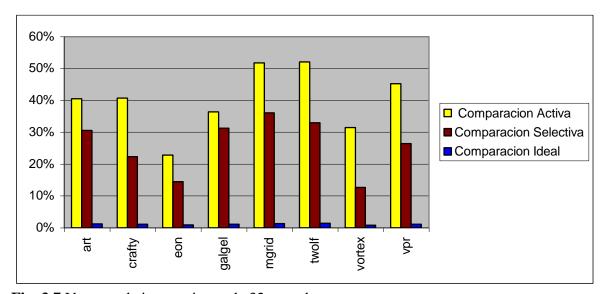

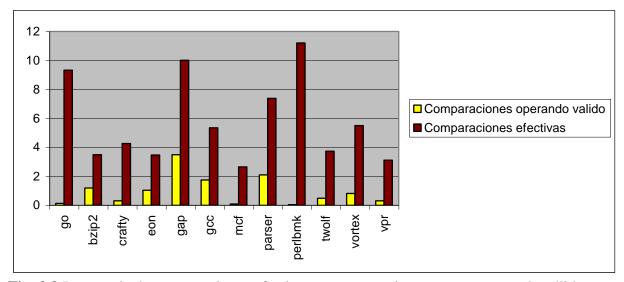

| Figura 3.8 Porcentaje de comparaciones efectivas y comparaciones con un oper         |                 |

| válido dentro de la ventana de instrucciones (SPECINT)                               |                 |

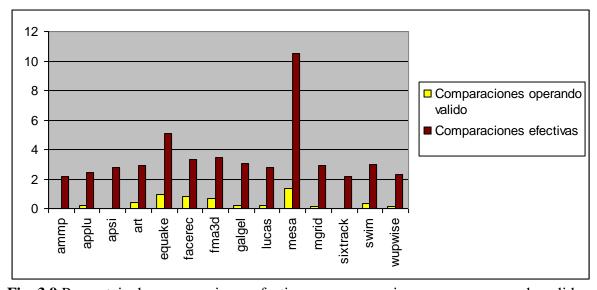

| Figura 3.9 Porcentaje de comparaciones efectivas y comparaciones con un oper         |                 |

| valido dentro de la IW (SPECFP)                                                      |                 |

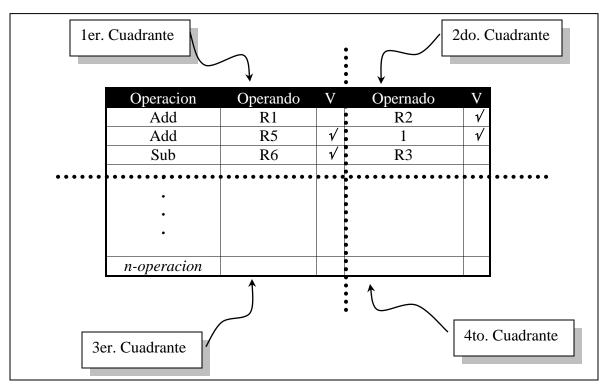

| Figura 3.10 Partición imaginaria de la ventana de instrucciones                      |                 |

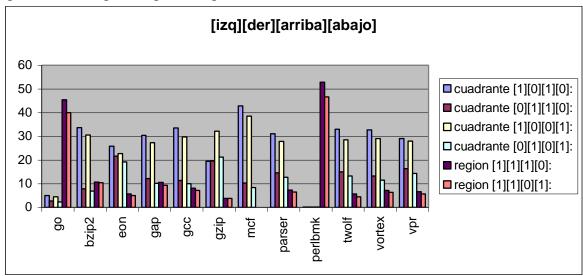

| Figura 3.11 Porcentaje de receptores (operandos) por cuadrante en la ventana (SPEC   |                 |

| Eigene 2.12 Demonstrie de moonstrang (oppendes) per guadrente en la ventana (SDE     |                 |

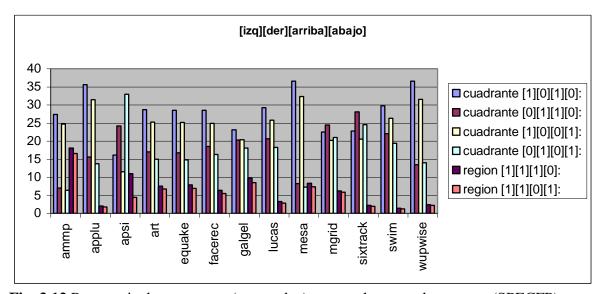

| Figura 3.12 Porcentaje de receptores (operandos) por cuadrante en la ventana (SPE    |                 |

| Fig. 3.13 Potencia consumida en ventanas de instrucciones con diferente númer        |                 |

| entradas (Watts)                                                                     |                 |

| Figura 3.14 Esquema <i>Direct Tag Search</i> (DTS)                                   | <i>52</i><br>55 |

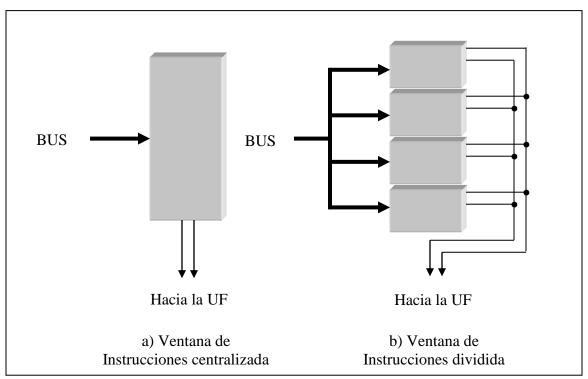

| Figura 3.15 Ventana de instrucciones dividida en bloques                             |                 |

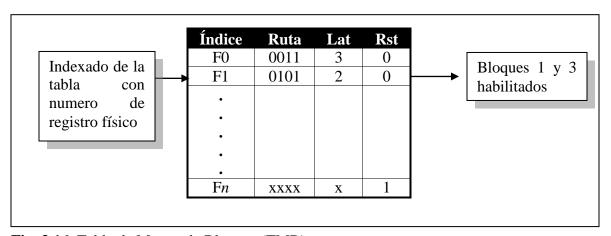

| Figura 3.16 Tabla de Mapeo de Bloques (TMB)                                          |                 |

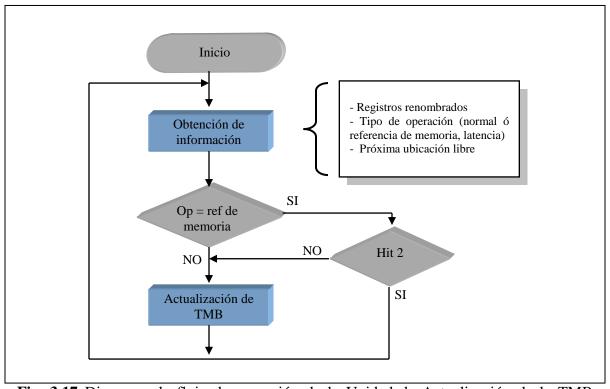

| Figura 3.17 Diagrama de flujo de operación de la Unidad de Actualización de la       |                 |

| (UAT)                                                                                |                 |

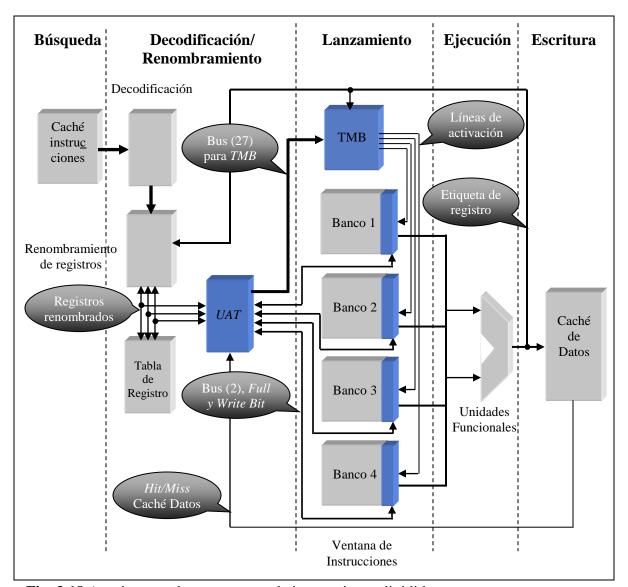

| Figure 3.18 Arquitecture de una ventana de instrucciones dividida                    |                 |

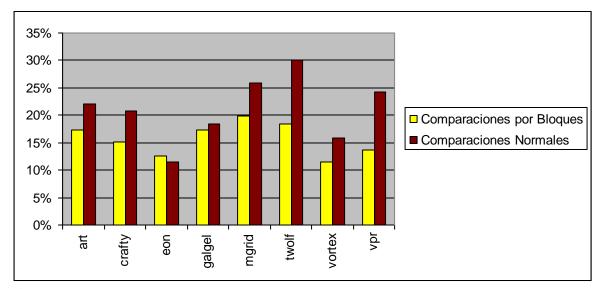

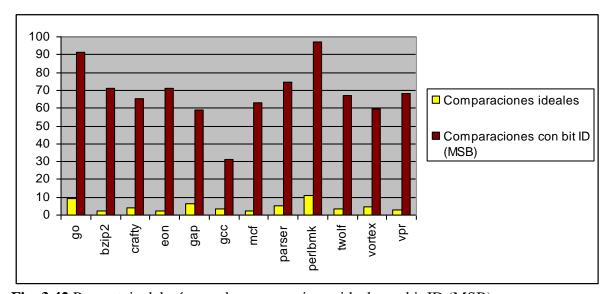

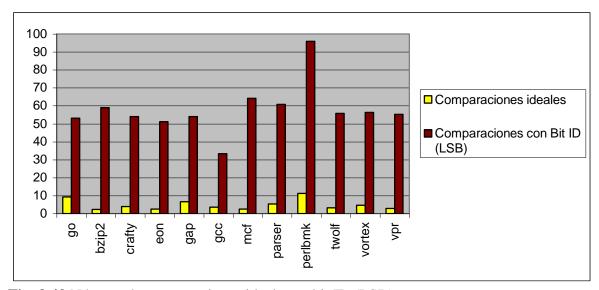

| Figura 3.19 Número de comparaciones de esquema normal vs por bloques (política                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ı de |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| comparación activa) ventana de 64 entradas, dividida en 4 bloques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 62 |

| Figura 3.20 Número de comparaciones esquema normal vs por bloques (política                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | de   |

| comparación activa) ventana de32 entradas, dividida en 4 bloques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 62 |

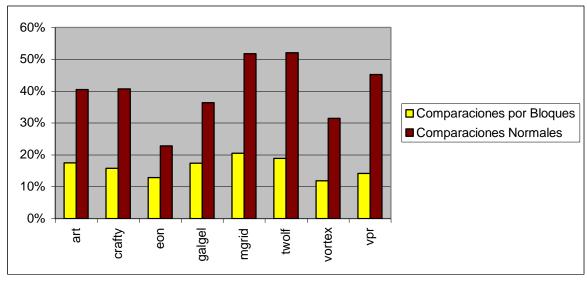

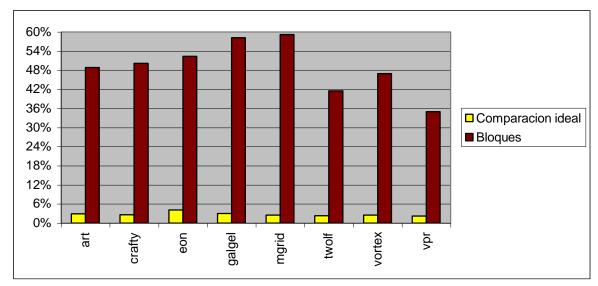

| Figura 3.21 Número de comparaciones ideales vs por bloques (política de comparaciones de co |      |

| arbitraria) ventana de 64 entradas, dividida en 4 bloques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

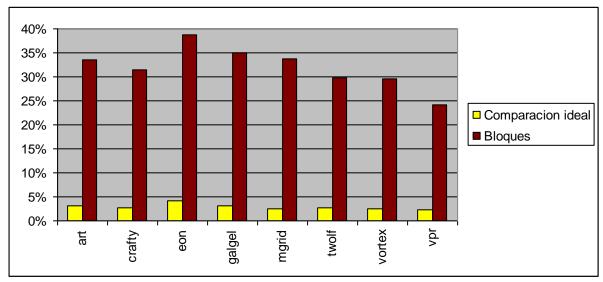

| Figura 3.22 Número de comparaciones ideales vs por bloques (política de comparaciones ideales vs por bloques ideales vs por bloques ideales vs por bloques (política de comparaciones ideales vs por bloques ideales vs por blo |      |

| arbitraria) ventana de 32 entradas, dividida en 4 bloques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

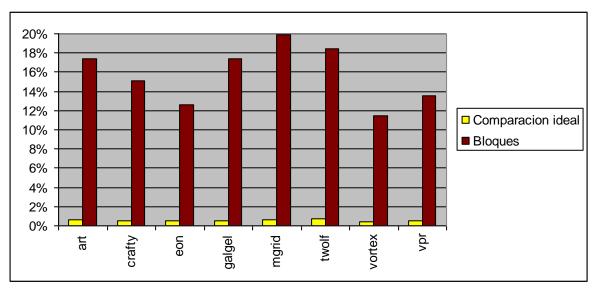

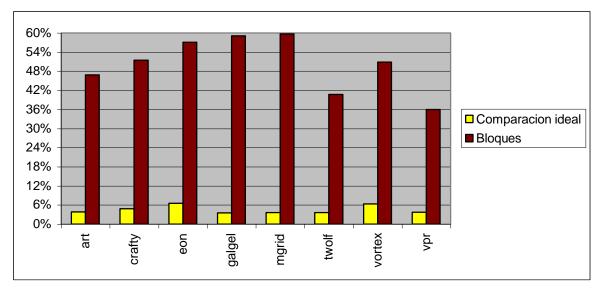

| Figura 3.23 Número de comparaciones ideales vs bloques (política de comparaciones de compar |      |

| activa) ventana de64 entradas, dividida en 4 bloques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

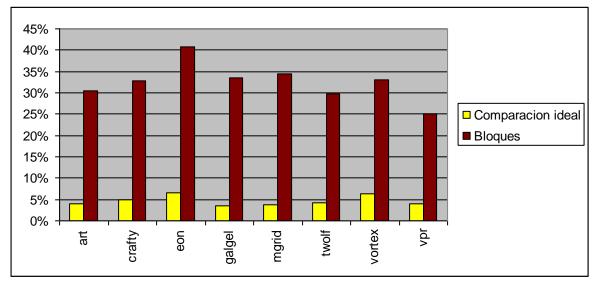

| Figura 3.24 Número de comparaciones ideales vs bloques (política de comparaciones de compar |      |

| activa) ventana de32 entradas, dividida en 4 bloques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

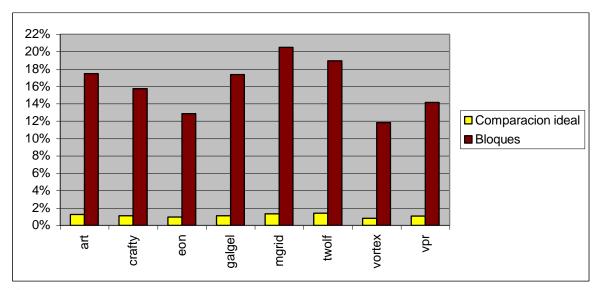

| Figura 3.25 Número de comparaciones ideales vs. Bloques (política de comparaciones)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ión  |

| selectiva) ventana de64 entradas, dividida en 4 bloques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| Figura 3.26 Número de comparaciones ideales vs. Bloques (política de comparaciones)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| selectiva) ventana de 32 entradas, dividida en 4 bloques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

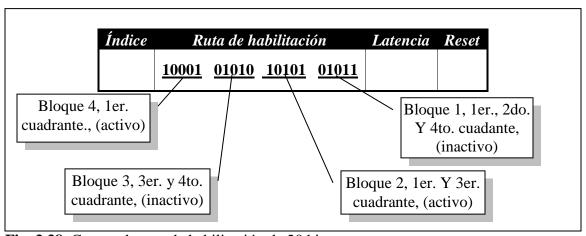

| Figura 3.27 División de bloques de la ventana de instrucciones en columnas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| Figura 3.28 Formato de los campos de la TMB para bloques divididos en columnas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

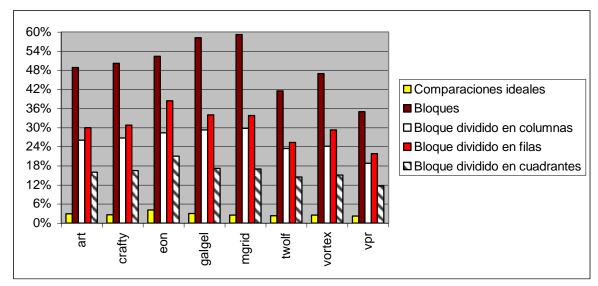

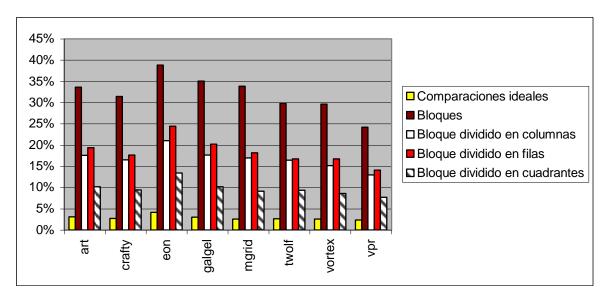

| Figura 3.29 Número de comparaciones ideales, por bloques y bloques divididos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| columnas (ventana de 64 entradas)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| Figura 3.30 Número de comparaciones ideales, bloques y bloques divididos en colum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| (ventana de 32 entradas)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Figura 3.31 División de Bloques en Filas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Figura 3.32 Campos de la TMB para submodelo de División de Bloques en Filas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Figura 3.33 Número de comparaciones ideales, por bloques y bloques divididos en f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| (ventana de 64 entradas)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Figura 3.34 Número de comparaciones ideales, por bloques y bloques divididos en f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| (ventana de 32 entradas)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71   |

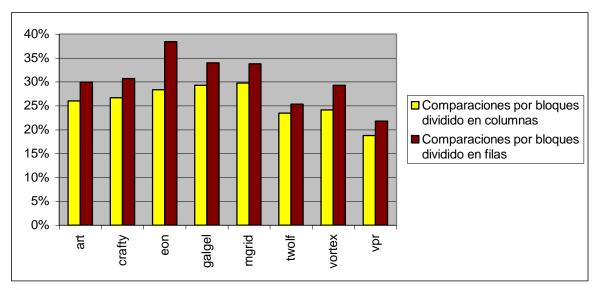

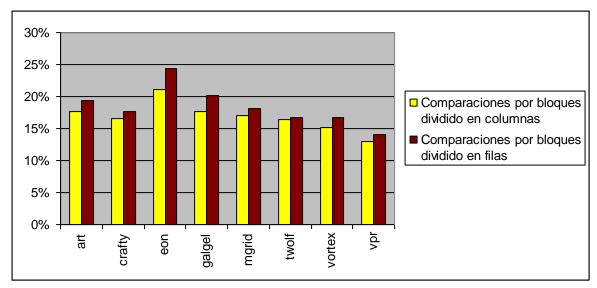

| Figura 3.35 Número de comparaciones de bloques divididos en columnas vs bloq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| divididos en filas (ventana de 64 entradas)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Figura 3.36 Número de comparaciones de bloques divididos en columnas vs bloq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| divididos en filas (ventana de 32 entradas)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •    |

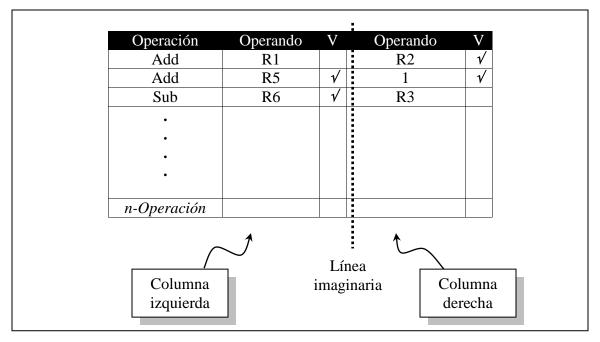

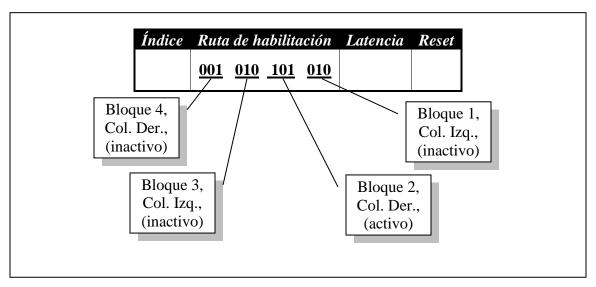

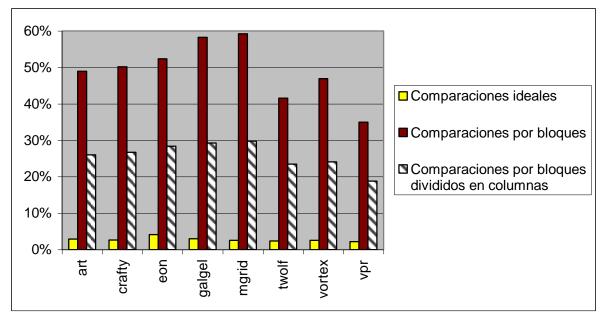

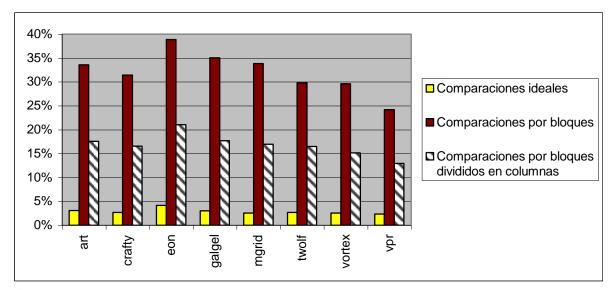

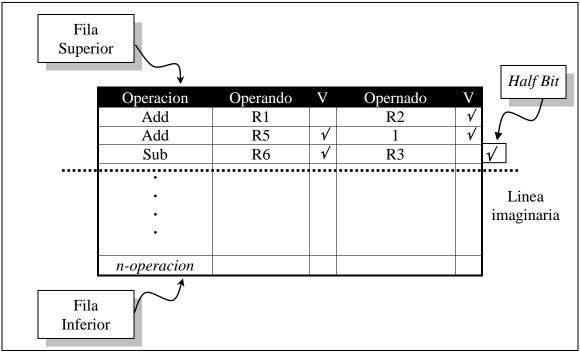

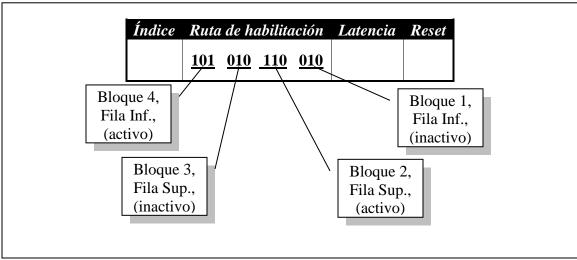

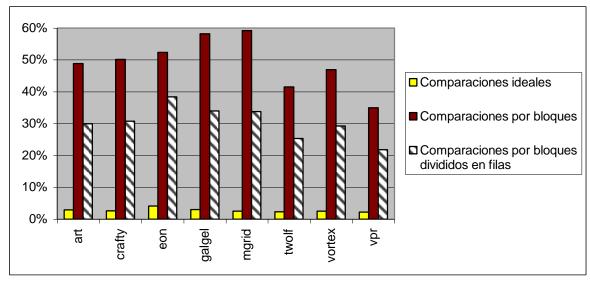

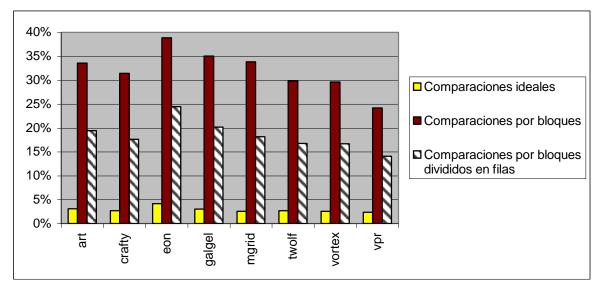

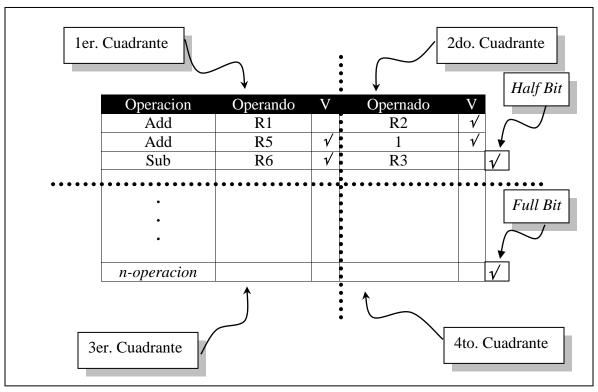

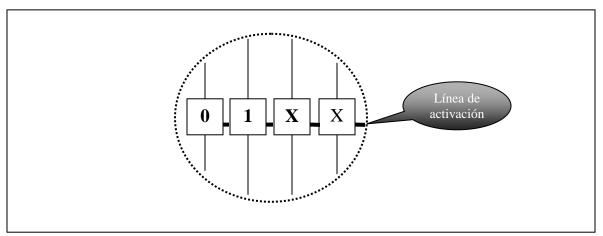

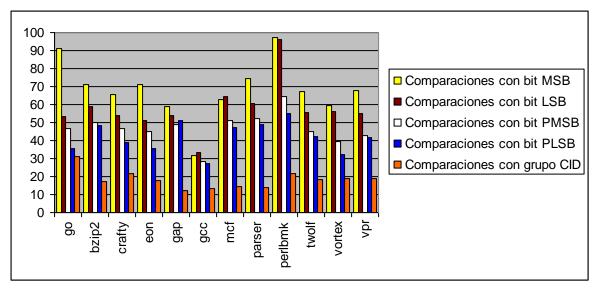

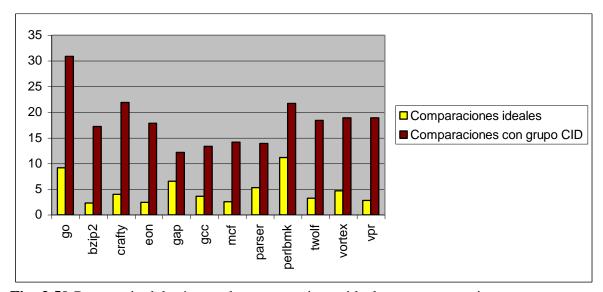

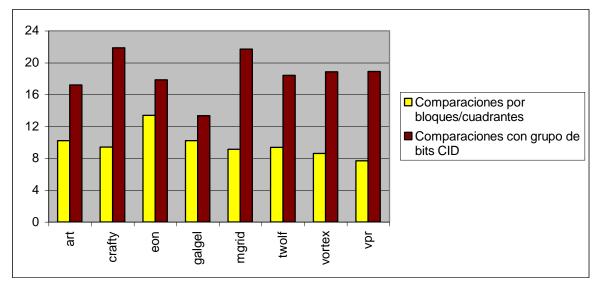

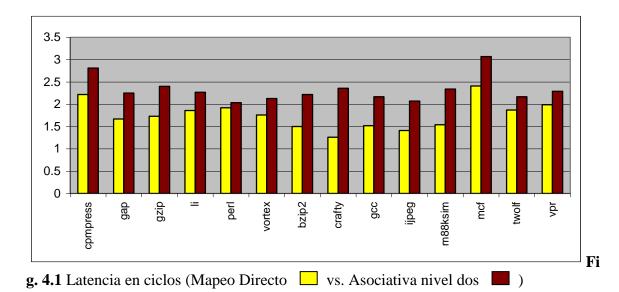

| Figura 3.37 Partición imaginaria de la ventana de instrucciones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |